【会员论文】南邮唐为华教授、郭宇锋教授&北邮李培刚教授&内蒙古大学团队:正向偏压应力下p-NiO/n-Ga₂O₃异质结势垒肖特基二极管性能退化的研究

日期:2026-04-03阅读:27

由南京邮电大学唐为华教授、郭宇锋教授、季学强副教授、北京邮电大学李培刚教授、内蒙古大学刘增研究员等人的研究团队在学术期刊IEEE TRANSACTIONS ON ELECTRON DEVICES发布了一篇名为Insight Into the Performance Degradation of p-NiO/n-Ga₂O₃ Heterojunction Barrier Schottky Diode Under Forward Bias Stress( 正向偏压应力下p-NiO/n-Ga₂O₃异质结势垒肖特基二极管性能退化的研究)的文章。

背 景

β-Ga₂O₃因约4.9 eV的超宽禁带、8 MV/cm的超高电场强度,以及远优于硅的巴利加优值(BFOM,Baliga’s figure of merit),在高压大功率电子器件中具备巨大应用潜力。该材料衬底制备的熔体法成本低,有商用大尺寸导电衬底,且n型掺杂外延技术成熟,是下一代功率半导体的优选材料,但p型Ga₂O₃的缺失严重限制了双极器件的发展,单极型Ga₂O₃肖特基势垒二极管(SBD,Schottky Barrier Diode)成为首批拟应用于功率电子系统的Ga₂O₃基器件。氧化镍(NiO)作为p型半导体,带隙3.4-4 eV、临界电场2-5 MV/cm,由其构建的p-NiO/n-Ga₂O₃异质结势垒肖特基二极管(HJBS,Heterojunction Barrier Schottky)实现了千伏级性能,大电流应用表现优异,静态性能媲美商用功率器件。但现有研究多聚焦SBD正向偏置应力下的界面态积累,HJBS需同时考虑肖特基接触和NiO/Ga₂O₃异质结界面态,且对其界面特性和退化机理的认知不足,因此该团队开展了HJBS在不同温度下正向偏置应力的退化与恢复行为研究。

主要内容

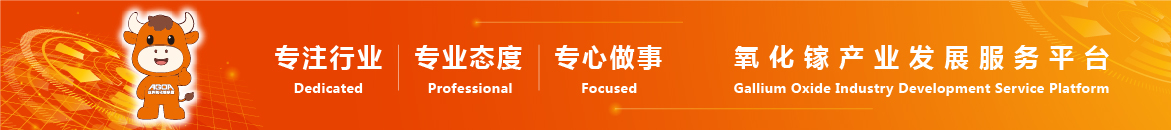

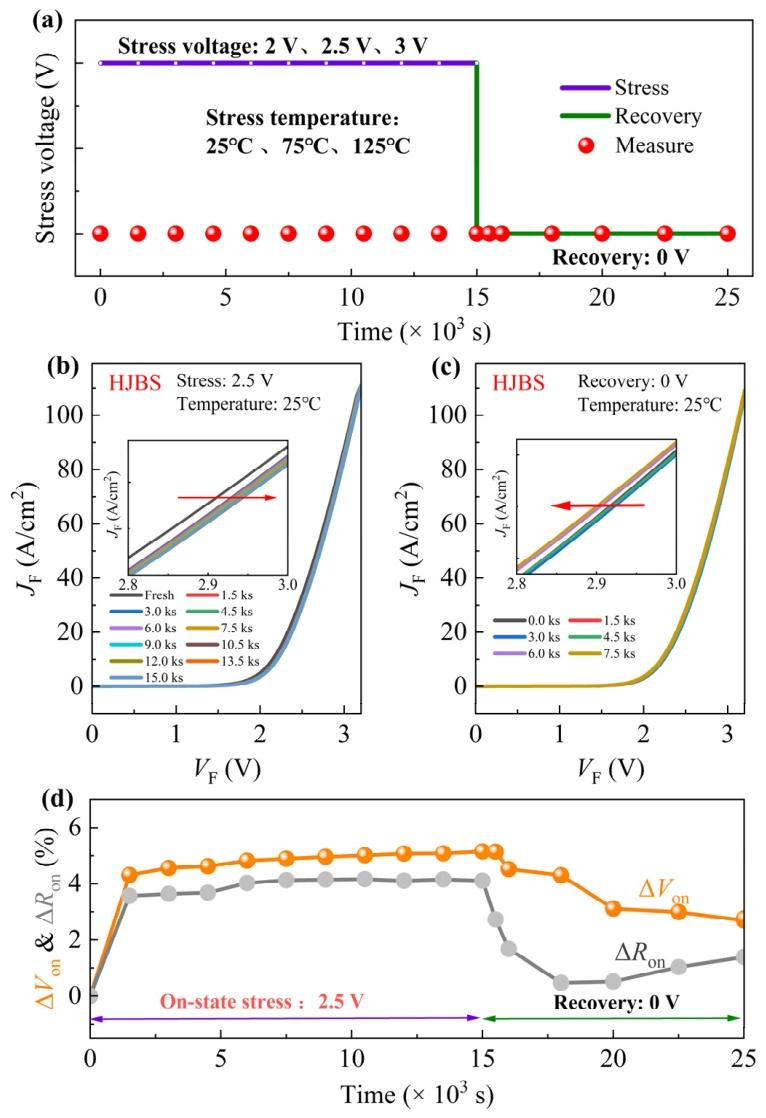

该团队系统研究了p-NiO/n-Ga₂O₃异质结势垒肖特基二极管(HJBS)在高温正向偏置(HTFB)应力下的退化与恢复行为,并结合器件直流特性的退化趋势分析了其内在退化机理。所制备的基于p-NiO/n-Ga₂O₃异质结的HJBS器件表现出优异的电学性能,击穿电压超过1 kV,导通电阻为9.23 mΩ·cm²。但器件在实际电路工作中不可避免会受到高温、大电流应力作用,导致开启电压和导通电阻出现显著退化,这对HJBS器件的可靠性提出了更高要求。该团队对器件进行了正向偏置应力测试及后续的恢复性能评估,在25 ℃、2.5 V的正向偏置应力下持续15 ks后,器件开启电压变化量(ΔVₒₙ)仅出现5.2%的退化,该退化归因于施主陷阱相关的电子俘获效应。在后续的恢复阶段,ΔVₒₙ出现了2.7%的不可恢复退化,该团队认为这是由体材料内的缺陷补偿或钝化现象阻碍了被俘获电子的释放所导致。这些研究结果为提升Ga₂O₃功率器件的可靠性提供了重要参考。

创新点

1.测试方法创新:首次采用测量-应力-测量法(MSM,Measurement-Stress-Measurement),研究了β-Ga₂O₃基HJBS器件在不同温度正向偏置应力下的关键电学参数退化与恢复行为。

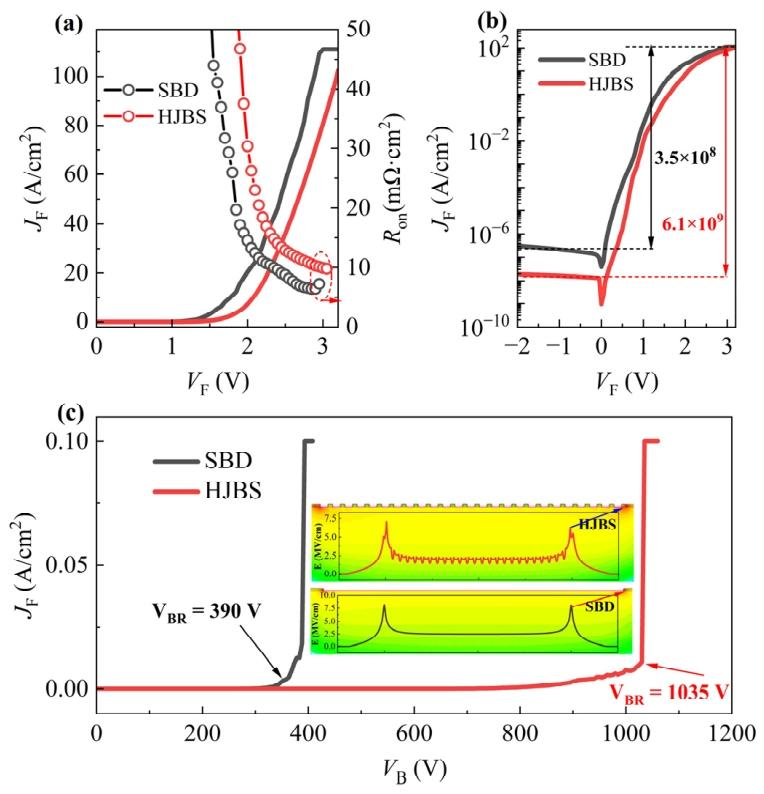

2.器件性能表征:制备的p-NiO/n-Ga₂O₃ HJBS器件击穿电压达1035 V,是传统Ga₂O₃ SBD器件的2.65倍,且导通电阻低至9.23 mΩ·cm²,漏电流更小,开关性能更优异。

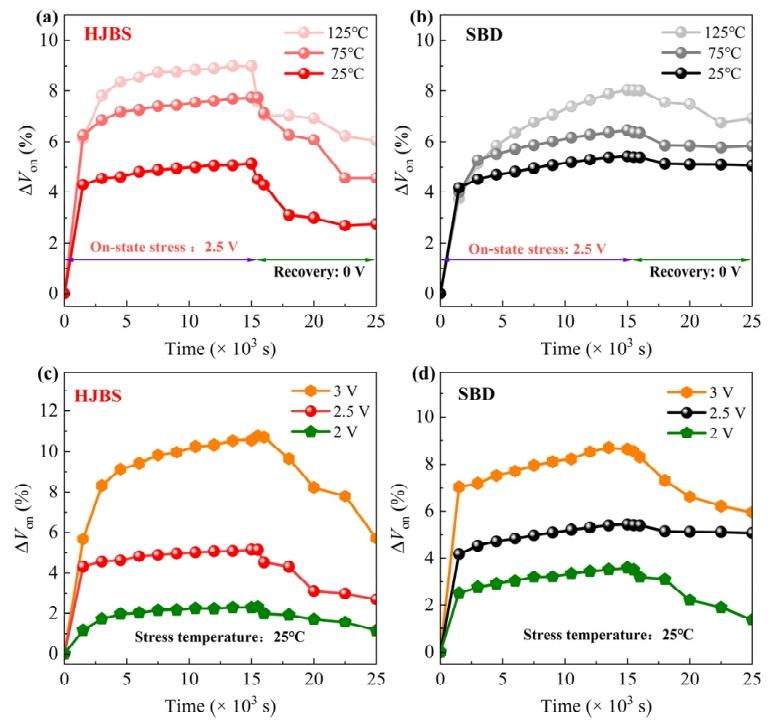

3.退化规律揭示:明确了温度和应力电压对HJBS与SBD器件开启电压退化的影响规律,高温和高应力电压会加剧器件的不可恢复退化,且HJBS的退化程度整体低于SBD。

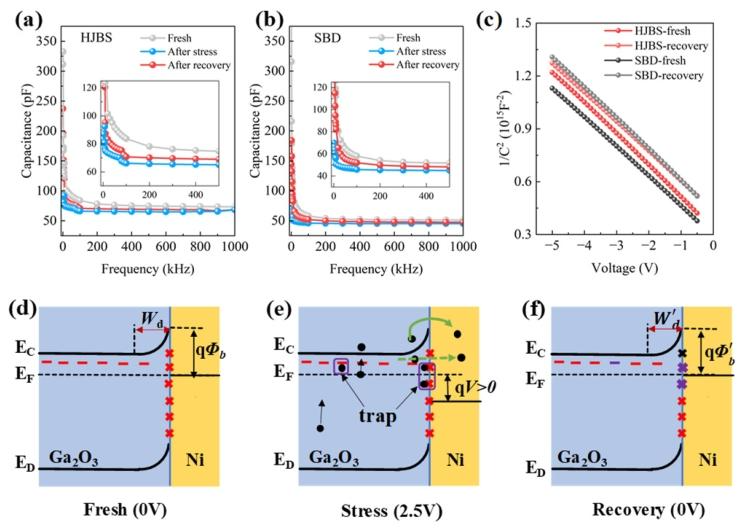

4.表征手段结合:结合电流-电压(J-V)、电容-频率(C-f)、电容-电压(C-V)测试表征,从电学特性变化角度分析器件退化与恢复的微观过程。

5.机理深度阐释:阐明了HJBS器件正向偏置应力下退化源于内部热负荷和缺陷处的电子俘获,不可恢复退化则由体材料中稳定的缺陷补偿/钝化机制导致。

6.应用价值明确:揭示了Ga₂O₃异质结的可靠性机理,为宽禁带功率电子器件的材料优化、缺陷调控及长期稳定性提升提供了理论指导。

总 结

该团队通过测量-应力-测量(MSM)技术,系统研究了p-NiO/n-Ga₂O₃异质结势垒肖特基二极管(HJBS)在正向应力下的性能退化及恢复机理。研究发现,正向偏置应力下器件开启电压(Vₒₙ)的上升主要归因于内部热负荷和缺陷位点的电子俘获。值得注意的是,研究发现了器件存在不可恢复的退化部分,这一现象表明体材料中存在稳定的缺陷补偿或钝化机制,该机制会永久性阻碍被俘获电荷载流子的完全释放。电流和电容表征(C-f、J-V)结果表明,正向偏置应力下的退化和恢复行为由受主型界面陷阱的俘获与发射过程的动态平衡引起,这些过程还参与了陷阱辅助隧穿(TAT,Trap-Assisted Tunneling)过程,随后载流子又被体陷阱俘获。这些研究结果阐明了Ga₂O₃异质结的可靠性机理,从而为通过材料和缺陷优化提升超宽禁带功率电子器件的长期稳定性提供了指导。

项目支持

该研究工作得到国家自然科学基金、江苏省前沿技术研究与开发计划、江苏省自然科学基金、南京邮电大学人才引进自然科学研究启动基金的部分资助。

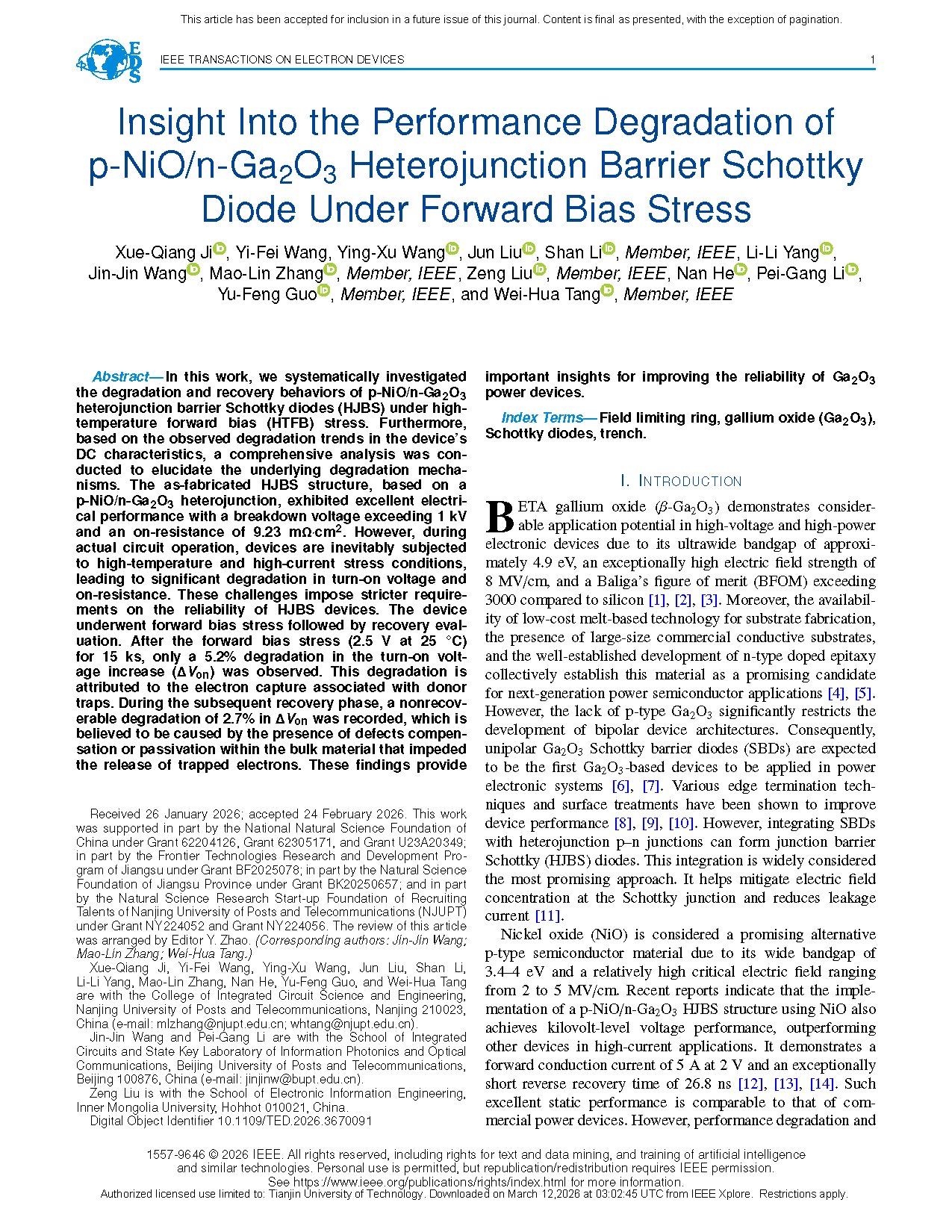

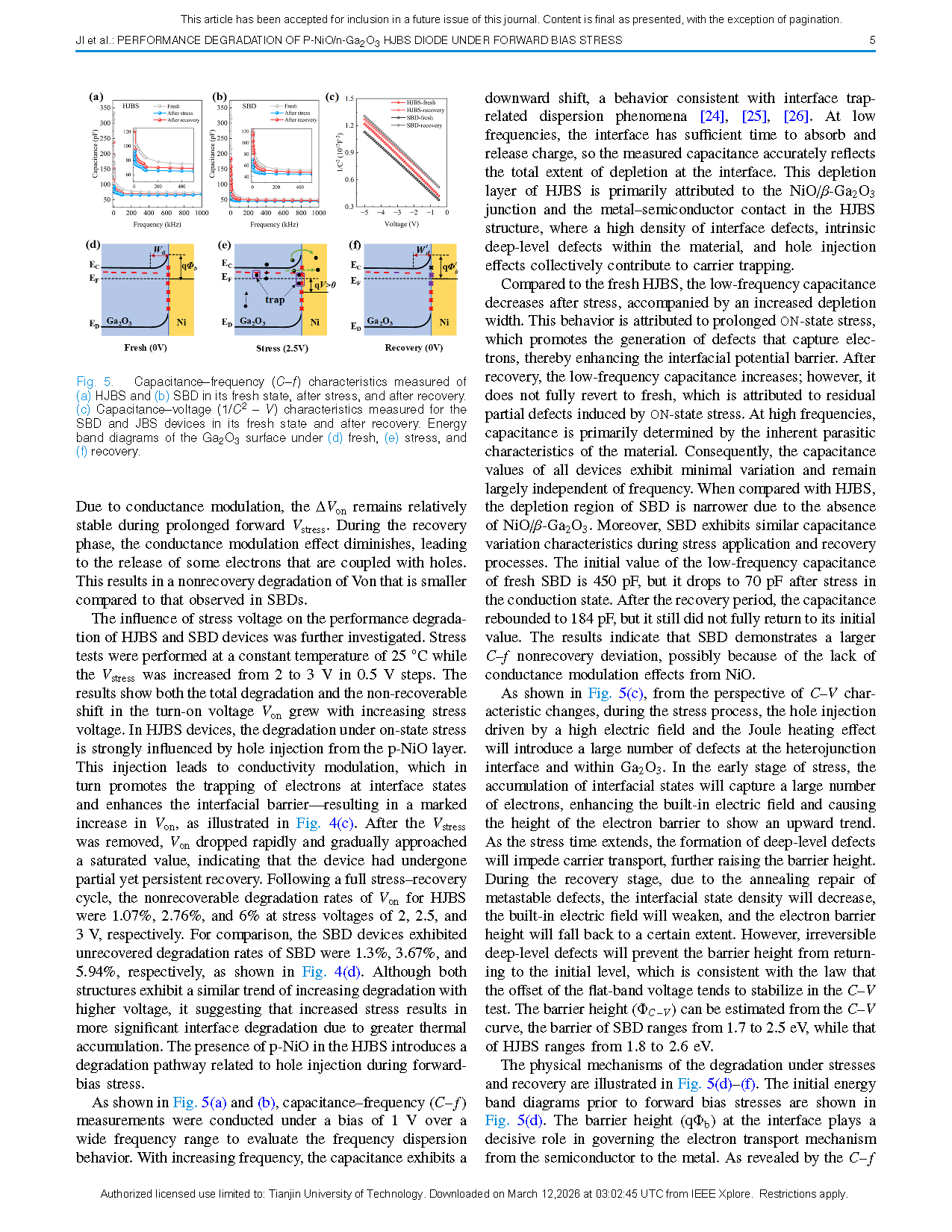

图1. (a) 异质结势垒肖特基二极管(HJBS)的结构示意图;(b) 异质结势垒肖特基二极管(HJBS)制备的关键工艺流程;(c) Ga₂O₃/NiO异质结对应的截面扫描电子显微镜(SEM)图像;(d) NiO表面的扫描电子显微镜(SEM)图像;(e) 氧化镓肖特基势垒二极管(SBD)的电容-电压(C-V)和电容倒数平方-电压(C⁻²-V)曲线

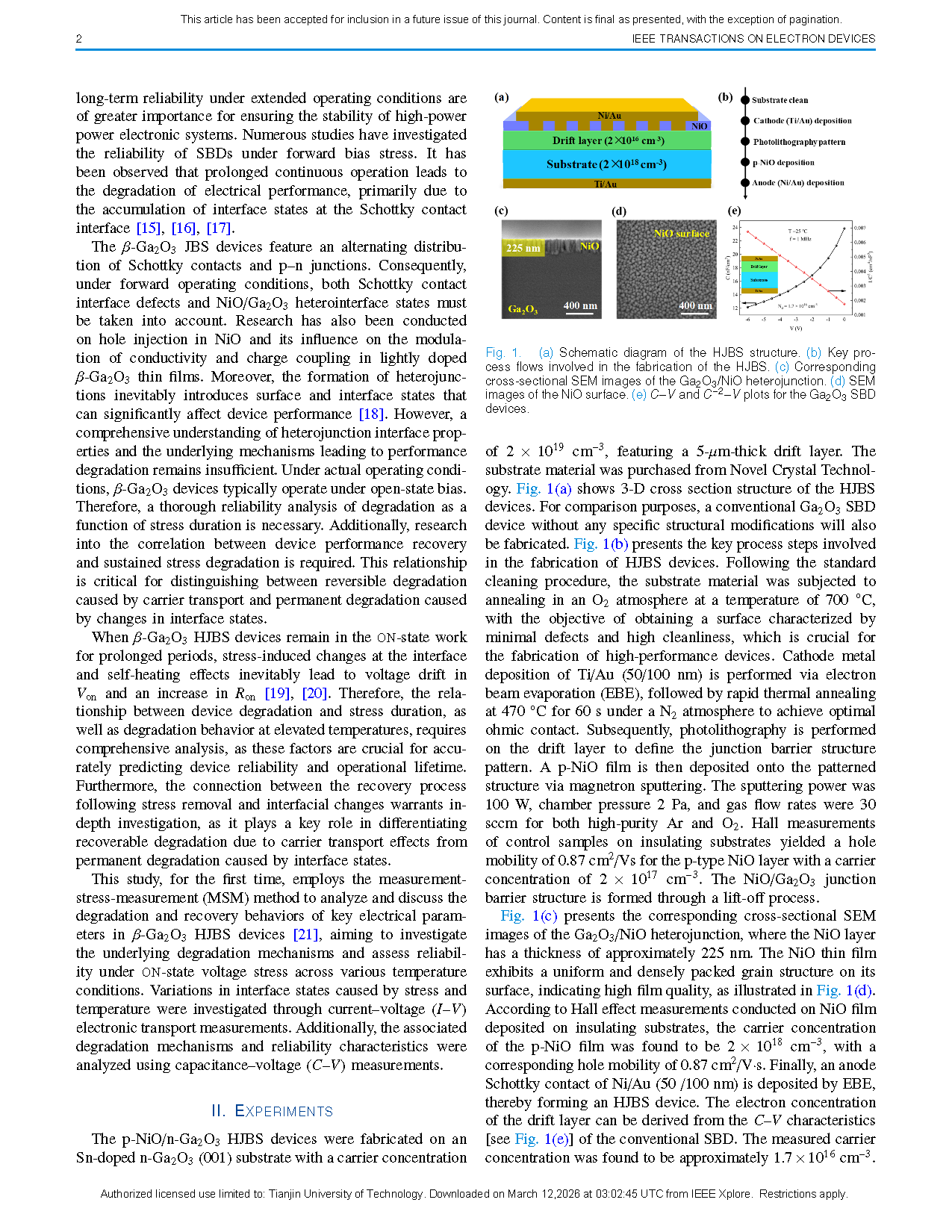

图2. (a) 两种器件的正向电流密度-电压特性及导通电阻随正向偏置电压的变化曲线;(b) 两种器件正向电流-电压的半对数曲线;(c) 两种不同结构器件的击穿特性及电场分布仿真图

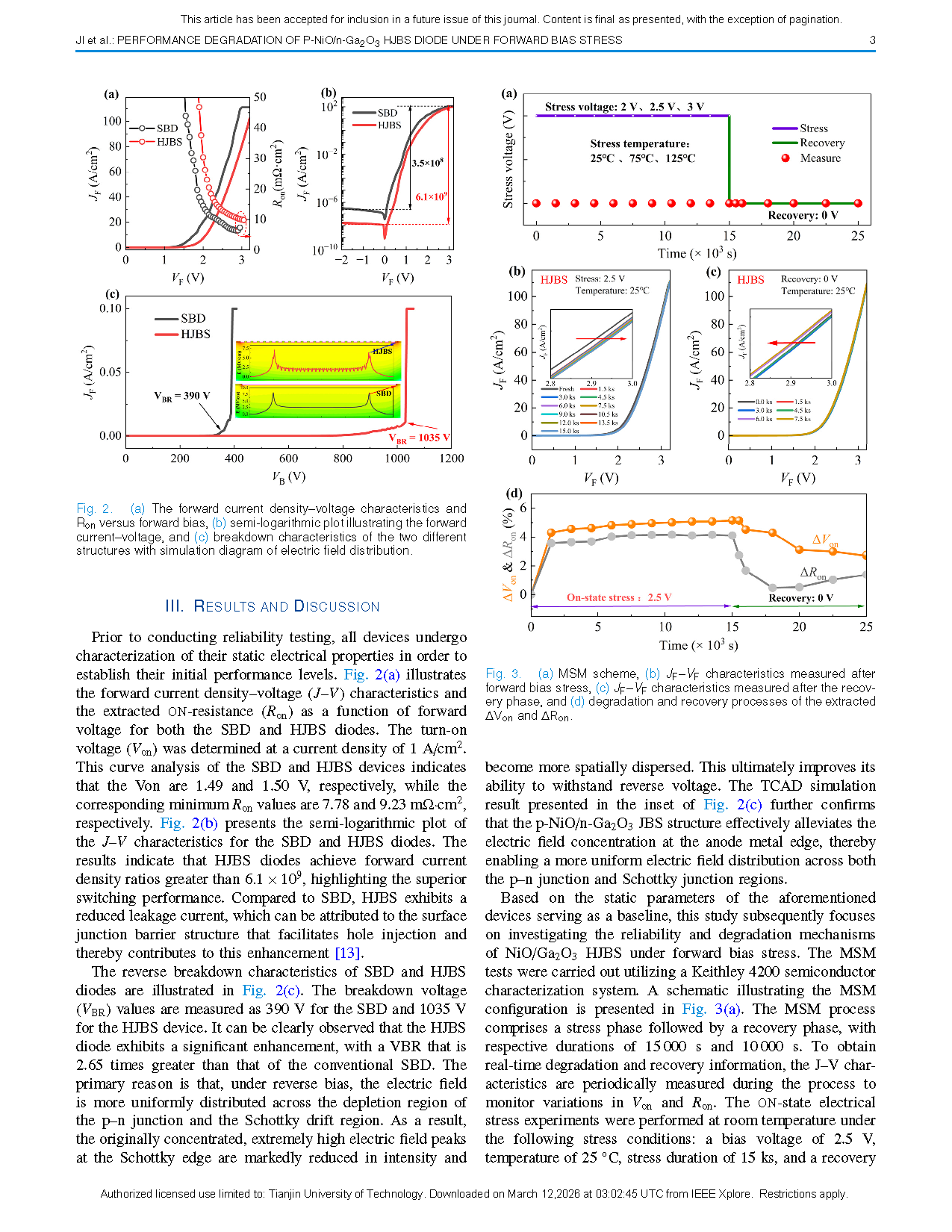

图3. (a) 测量-应力-测量(MSM)测试方案;(b) 正向偏置应力后测得的正向电流密度-正向电压(JF-VF)特性;(c) 恢复阶段后测得的正向电流密度-正向电压(JF-VF)特性;(d) 提取的开启电压变化量(ΔVₒₙ)和导通电阻变化量(ΔRₒₙ)的退化与恢复过程

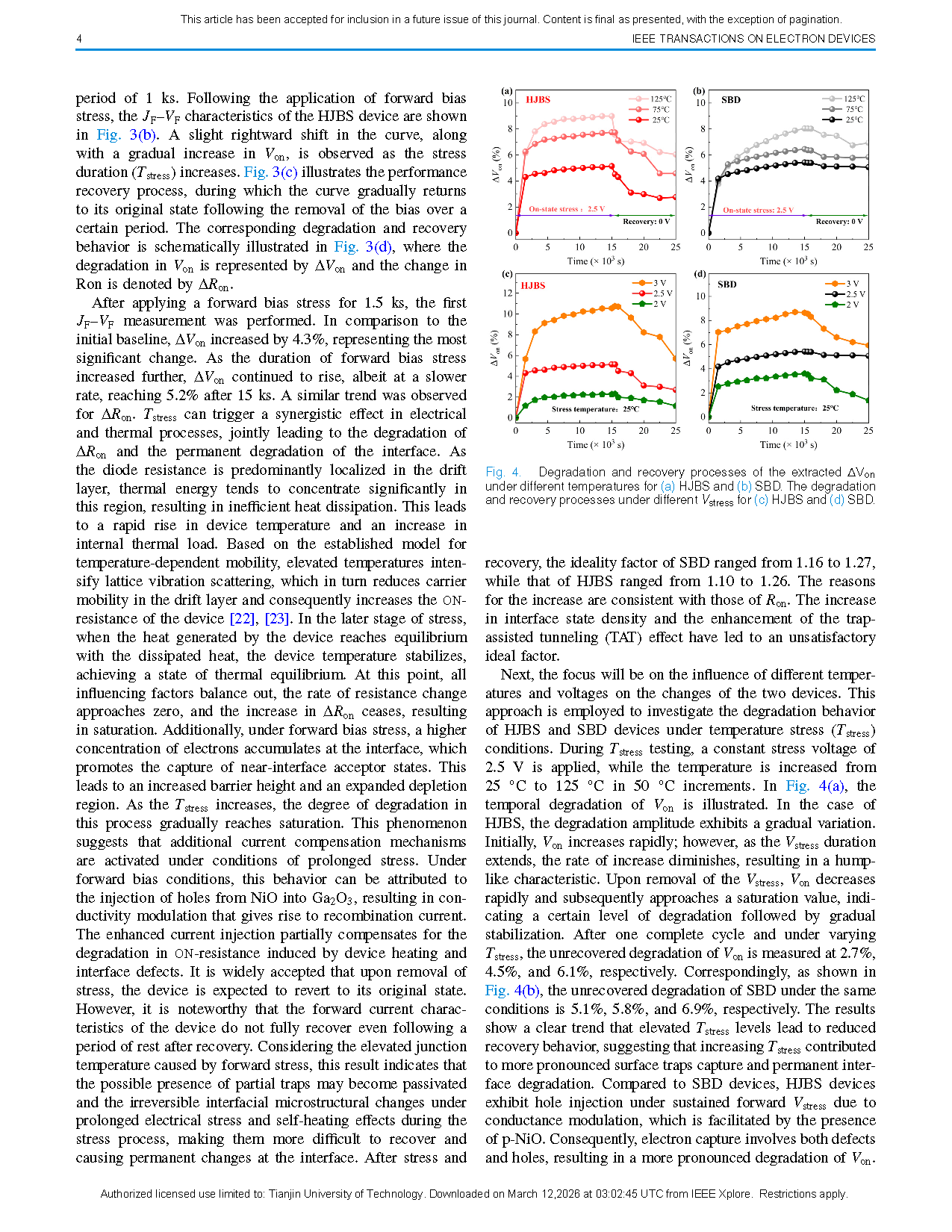

图4. 不同温度下提取的开启电压变化量(ΔVₒₙ)的退化与恢复过程:(a) 异质结势垒肖特基二极管(HJBS)、(b) 肖特基势垒二极管(SBD);不同应力电压下提取的开启电压变化量(ΔVₒₙ)的退化与恢复过程:(c) 异质结势垒肖特基二极管(HJBS)、(d) 肖特基势垒二极管(SBD)

图5. (a) 异质结势垒肖特基二极管(HJBS)、(b) 肖特基势垒二极管(SBD)在新鲜态、应力后和恢复后的电容-频率(C–f )特性;(c) 肖特基势垒二极管(SBD)和异质结势垒肖特基二极管(HJBS)在新鲜态和恢复后的电容-电压(1/C²-V)特性;Ga₂O₃表面在(d) 新鲜态、(e) 应力下、(f) 恢复后的能带图

DOI:

10.1109/TED.2026.3670091