【会员论文】西安理工大学胡继超副教授&西电彭博博士&深圳平湖实验室张道华院士:基于 Ga₂O₃/SiC pn 异质结 RESURF 结构的肖特基二极管研究

日期:2026-03-27阅读:189

由西安理工大学电子工程系胡继超副教授联合西安电子科技大学宽禁带半导体材料教育部重点实验室彭博博士联合国家宽禁带半导体技术创新中心(深圳)深圳平湖实验室张道华院士组成的研究团队在学术期刊Microelectronics Journal发布了一篇名为Research of Schottky diode based on Ga₂O₃/SiC pn heterojunction RESURF structure(基于 Ga₂O₃/SiC pn 异质结 RESURF 结构的肖特基二极管研究)的文章。

背 景

传统硅基器件受限于带隙宽度,性能已逼近理论极限,难以满足大功率电子器件对转换效率的持续需求。超宽禁带半导体 Ga₂O₃(氧化镓)凭借 4.5 ~ 4.9 eV 的带隙、8 MV/cm 的临界击穿场强、高饱和电子速度,以及可低成本制备大尺寸单晶衬底的优势,成为下一代功率器件的核心候选材料,其 Baliga 优值远超 GaN、SiC 与 Si 材料。但 Ga₂O₃ 存在难以实现有效 p 型掺杂、电子迁移率偏低、热导率极低且各向异性(0.1~0.27 W/cm·K)的问题,导致器件击穿电压未达理论值、易出现性能漂移与热累积失效。SiC(碳化硅)作为宽禁带半导体,可精准调控 p 型掺杂浓度,热导率高达 3.7~4.9 W/cm·K,与 Ga₂O₃ 异质集成能有效解决上述瓶颈。同时,降低表面电场(RESURF)技术可通过电荷共享优化电场分布,缓解击穿电压与导通电阻的权衡矛盾。该团队在 Ga₂O₃/SiC 异质外延研究基础上,提出集成异质结 pn 型 RESURF 结构的肖特基二极管,通过 TCAD 仿真优化器件性能。

主要内容

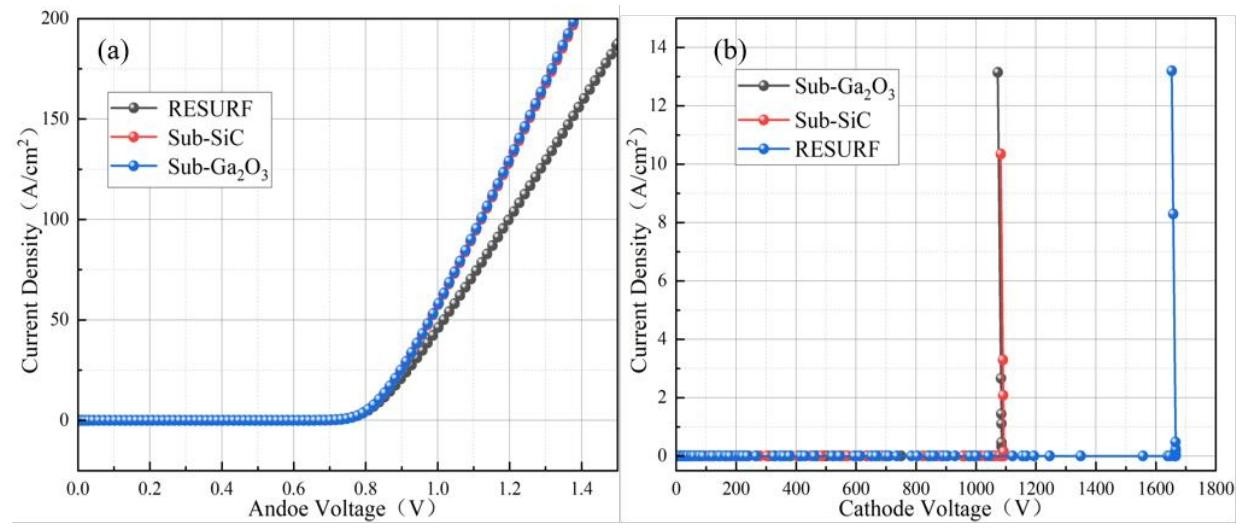

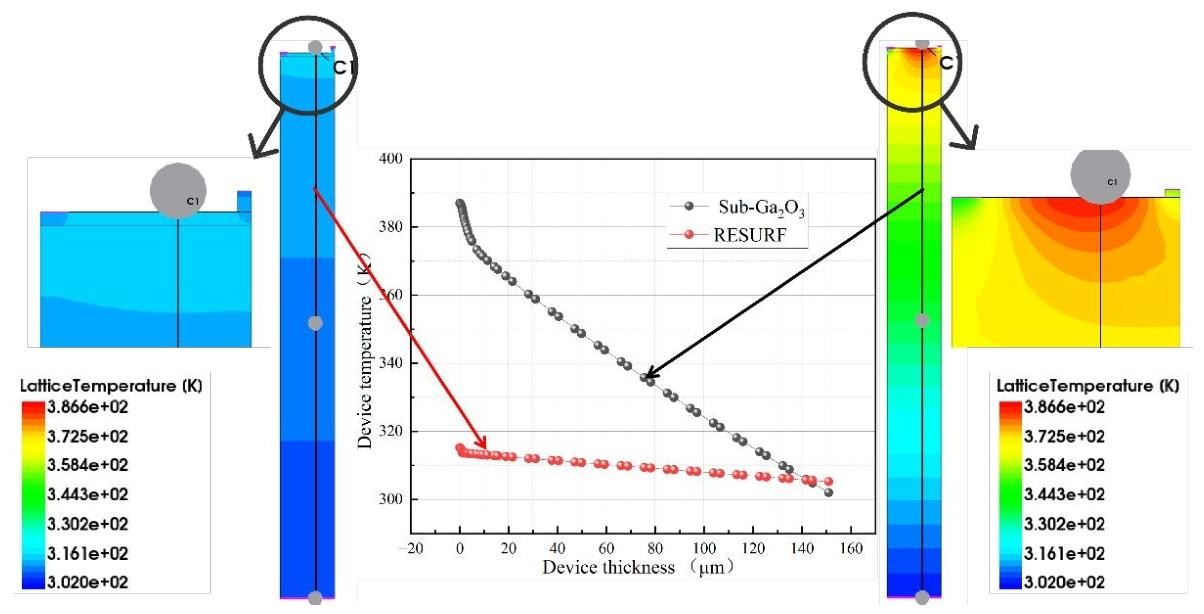

该团队报道了一种采用 p-SiC/n-Ga₂O₃ 异质结构成降低表面电场(RESURF)终端结构的肖特基二极管,利用 TCAD 仿真软件研究了器件特性。结果表明,该 RESURF 型肖特基势垒二极管(SBD)的比导通电阻(Ron,sp)为 25.604 mΩ·cm²,击穿电压提升至 1666 V,远高于 Ga₂O₃ 同质结器件的 1086 V,功率品质因数(PFOM)达到 0.108 GW/cm²。该团队系统研究了 n 型 Ga₂O₃ 漂移层厚度、p 型降场层(FDL)厚度及掺杂浓度对器件电学特性的影响。此外,器件自热效应导致的峰值温度从 387 K 降至 315 K,温度分布显著改善。该二极管利用 Ga₂O₃/SiC 异质结 pn 结构形成 RESURF 构型,提升了击穿电压与正向导通特性,同时采用高导热 SiC 衬底缓解了 Ga₂O₃ 材料热导率低的问题。

创新点

1. 结构创新:首次提出 Ga₂O₃/SiC pn 异质结耦合 RESURF 结构的肖特基二极管,突破传统 Ga₂O₃ 器件结构限制。

2. 性能提升:击穿电压从 1086 V 提升至 1666 V,功率品质因数达 0.108 GW/cm²,兼顾高耐压与低损耗。

3. 热管理优化:采用高导热 SiC 衬底,器件峰值温度降低 72 K,热分布更均匀,缓解自热效应。

4. 参数系统性优化:明确漂移层厚度、降场层厚度与掺杂浓度对器件性能的调控规律,获得最优击穿电压 1814 V。

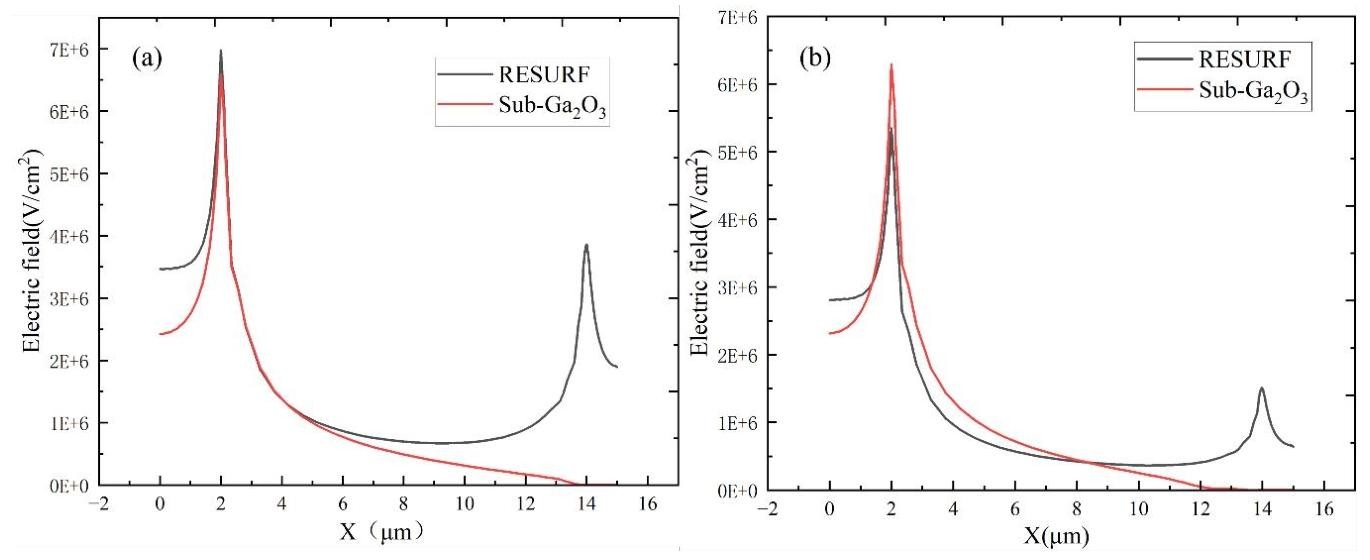

5. 机理明晰:揭示异质结垂直电场对表面电场的调制机制,解释 RESURF 结构提升耐压的核心原理。

结 论

针对 Ga₂O₃ 难以实现 p 型掺杂、热导率极低的核心难题,该团队提出集成 RESURF 技术的 Ga₂O₃ 基肖特基二极管。该器件实现 1666 V 击穿电压、25.604 mΩ·cm² 比导通电阻,功率品质因数达 0.108 GW/cm²;当漂移层厚度 0.9 μm、降场层厚度 1 μm、掺杂浓度 3×10¹⁶ cm⁻³ 时,击穿电压最高达 1812 V,比导通电阻 28.212 mΩ·cm²,功率品质因数 0.116 GW/cm²。器件温度分布显著优化,峰值温度从 387 K 降至 315 K。该团队系统分析了漂移层、降场层的厚度与掺杂浓度对器件特性的影响。但受漂移层厚度与掺杂浓度限制,阻断状态下漂移区未完全耗尽,导通损耗仍有优化空间。后续该团队将通过新增结构设计与几何参数优化,进一步提升器件耐压能力并降低导通损耗。

项目支持

该研究得到国家自然科学基金、西安市科协青年人才托举工程、西安市科技计划项目、陕西省青年科技新星项目、中国博士后科学基金项目的资助。

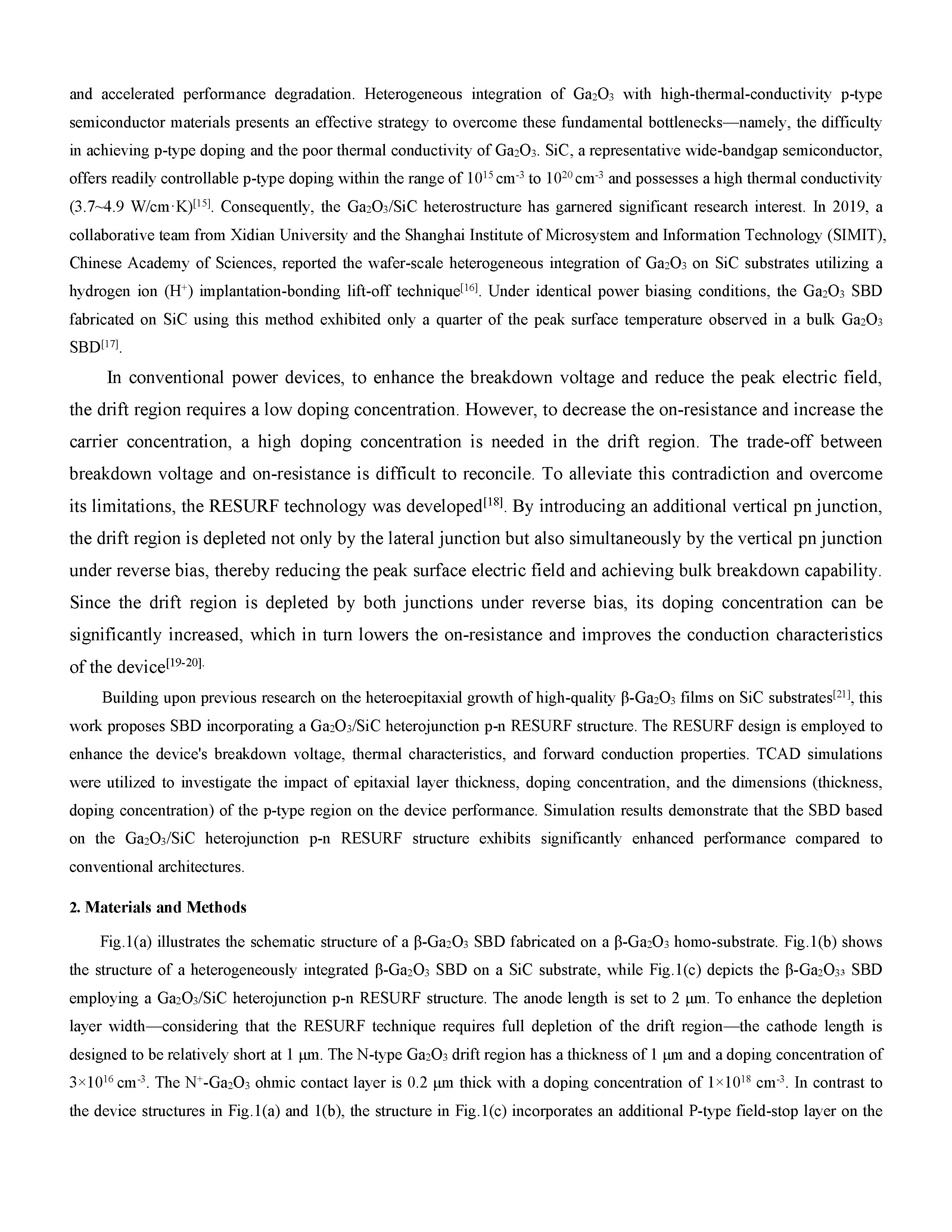

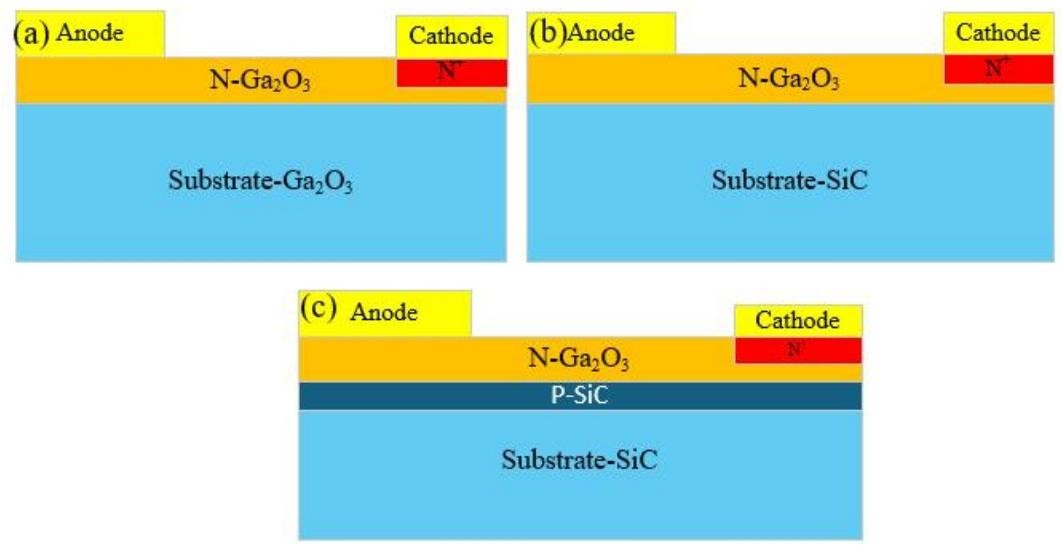

图1. 所研究的肖特基势垒二极管结构示意图:(a) 同质衬底上的 β-Ga₂O₃ 肖特基势垒二极管;(b) SiC 衬底上的 β-Ga₂O₃ 肖特基势垒二极管;(c) 具有 β-Ga₂O₃/SiC 异质结 RESURF 结构的 β-Ga₂O₃ 肖特基势垒二极管。

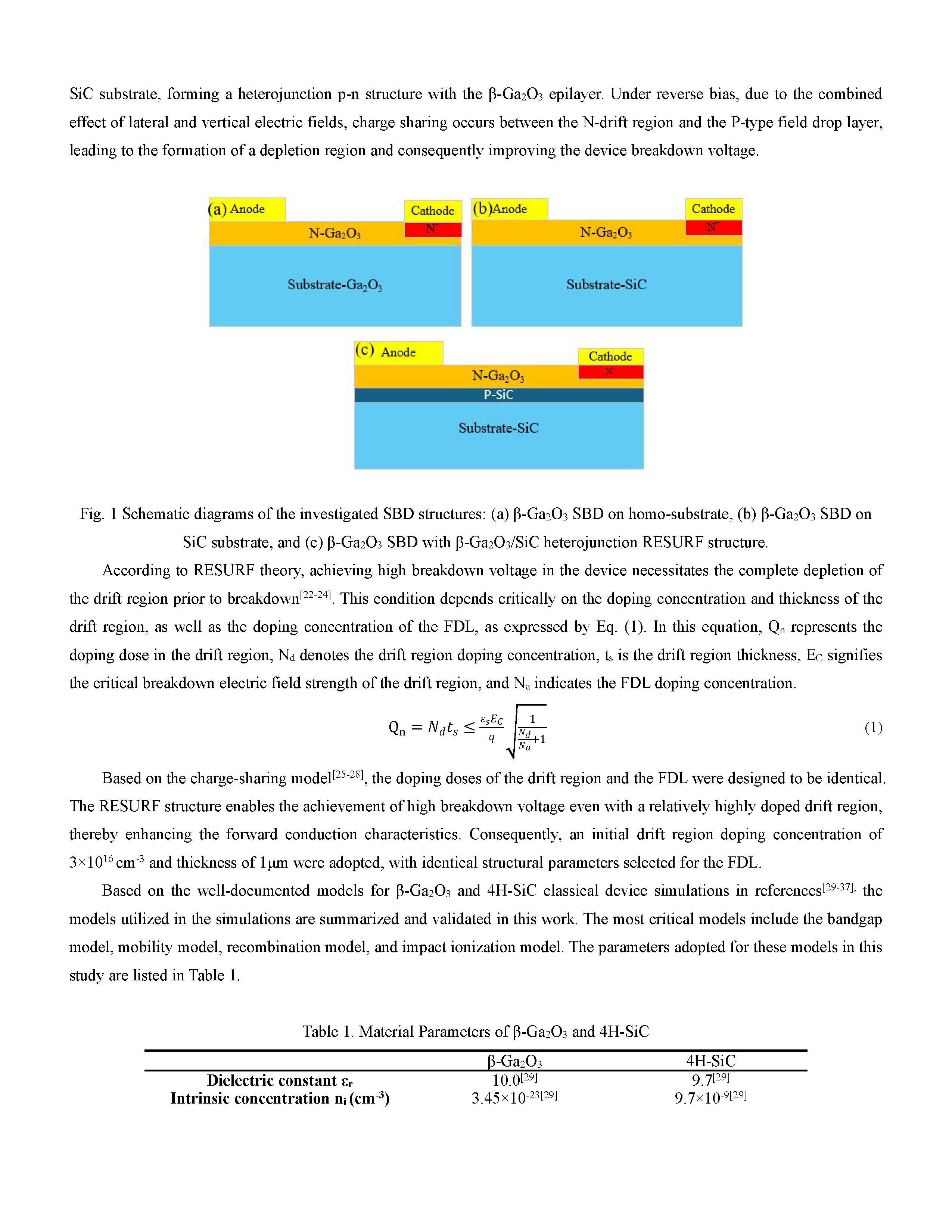

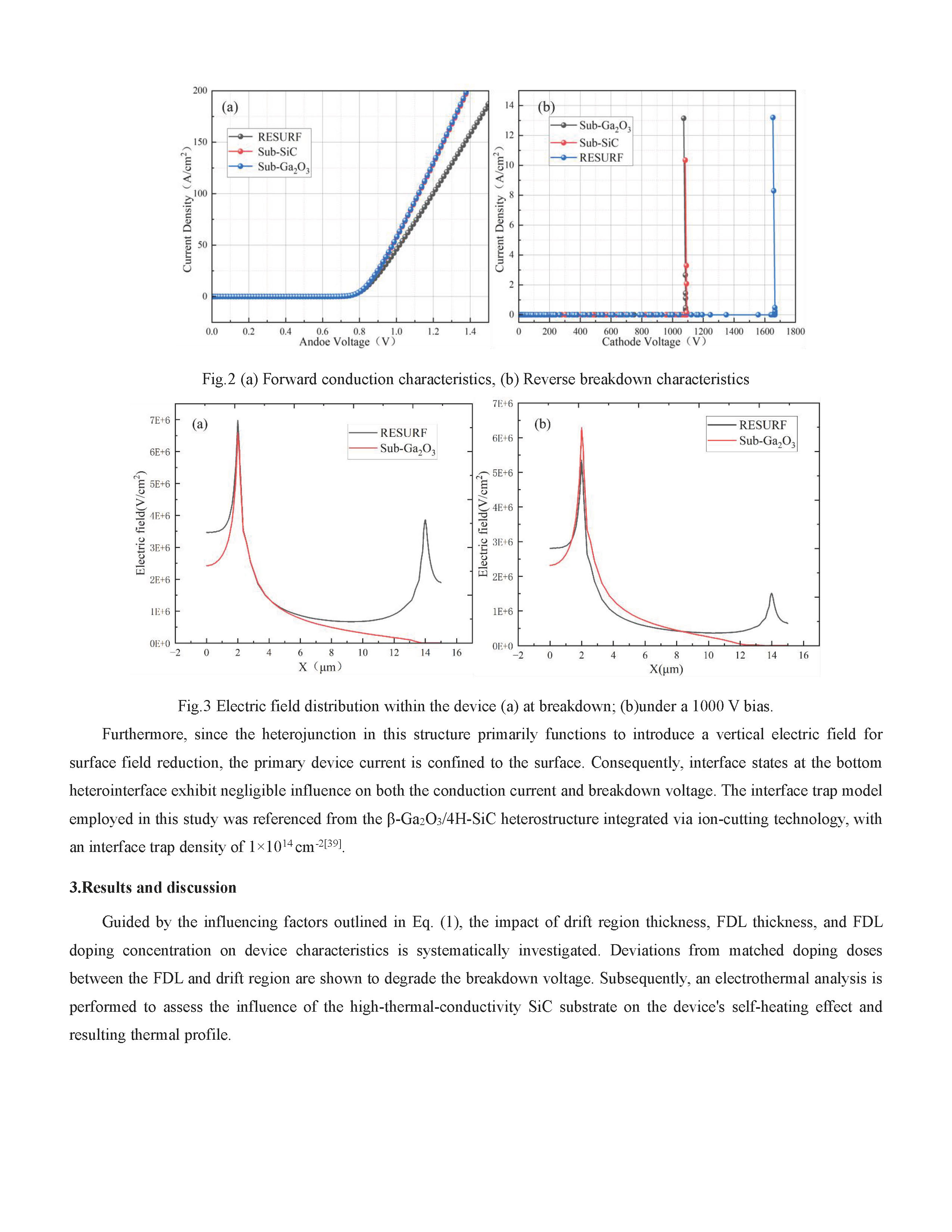

图2. (a) 正向导通特性;(b) 反向击穿特性。

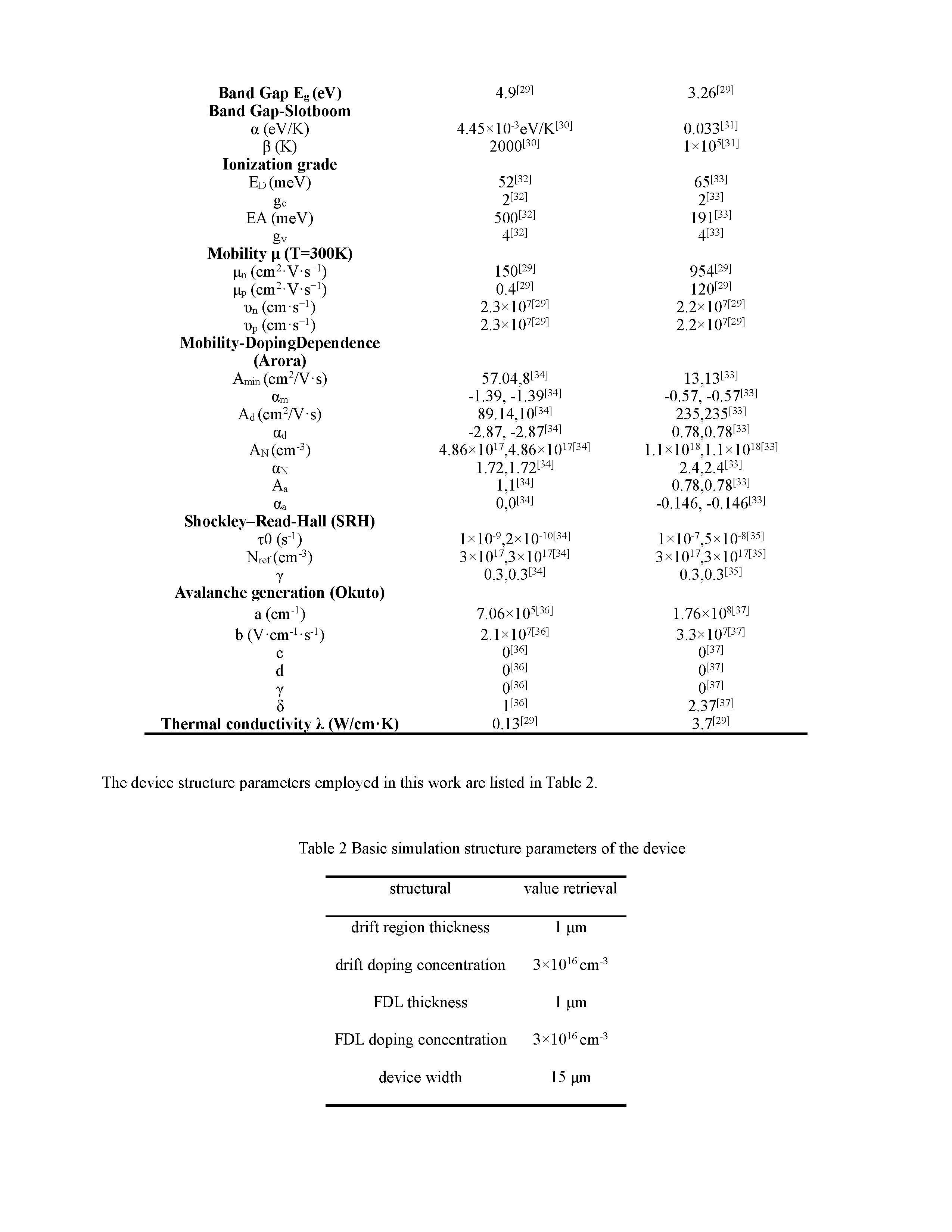

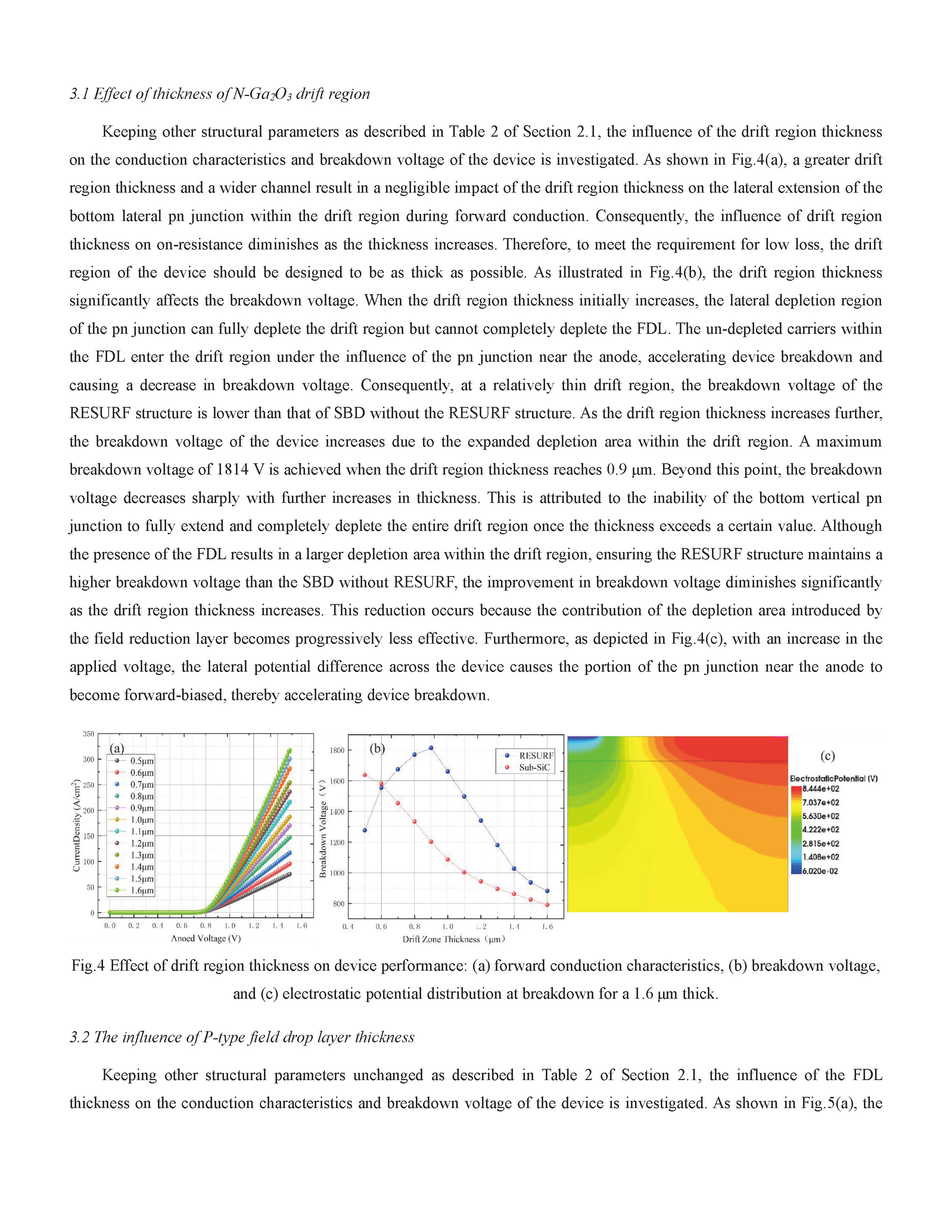

图3. 器件内部电场分布:(a) 击穿时;(b) 1000 V 偏置下。

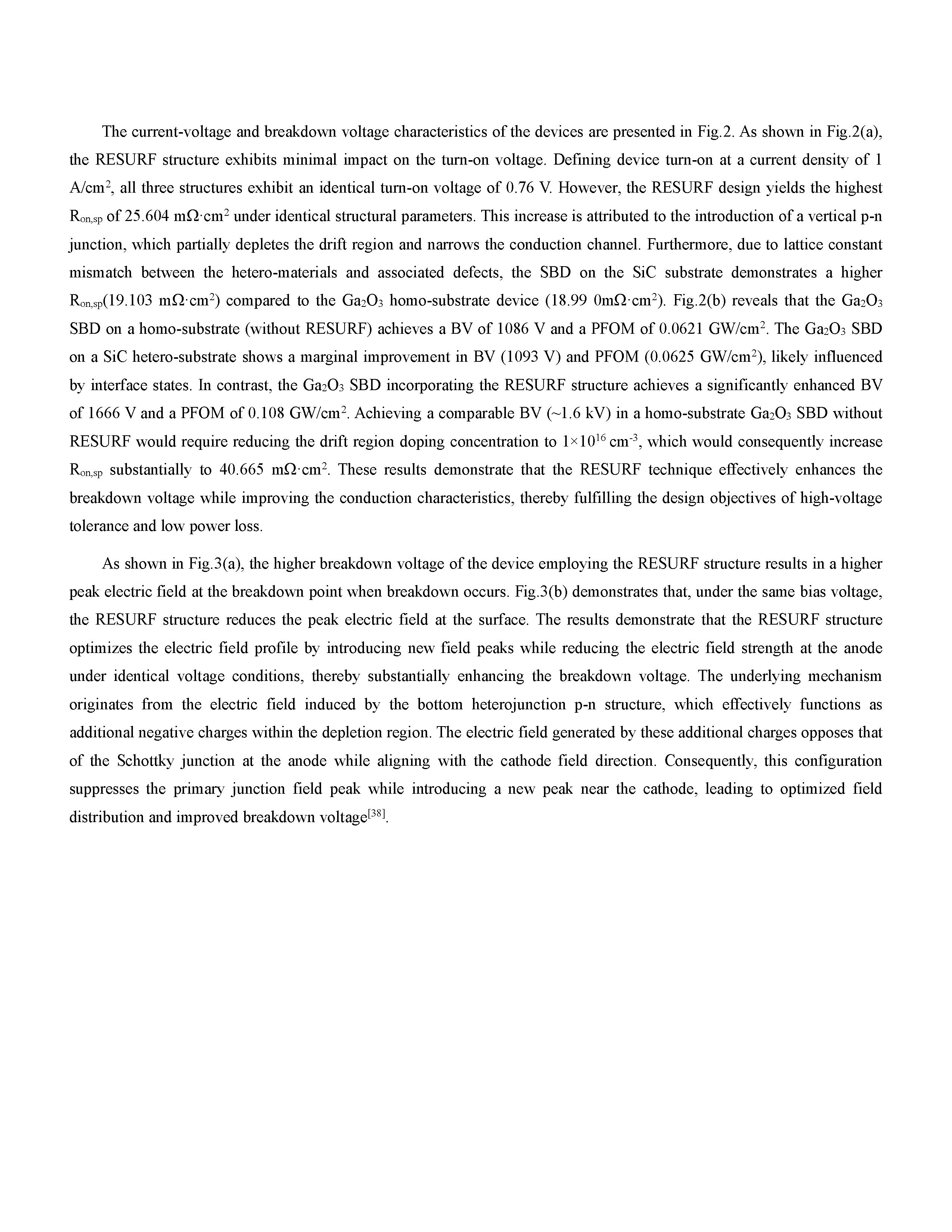

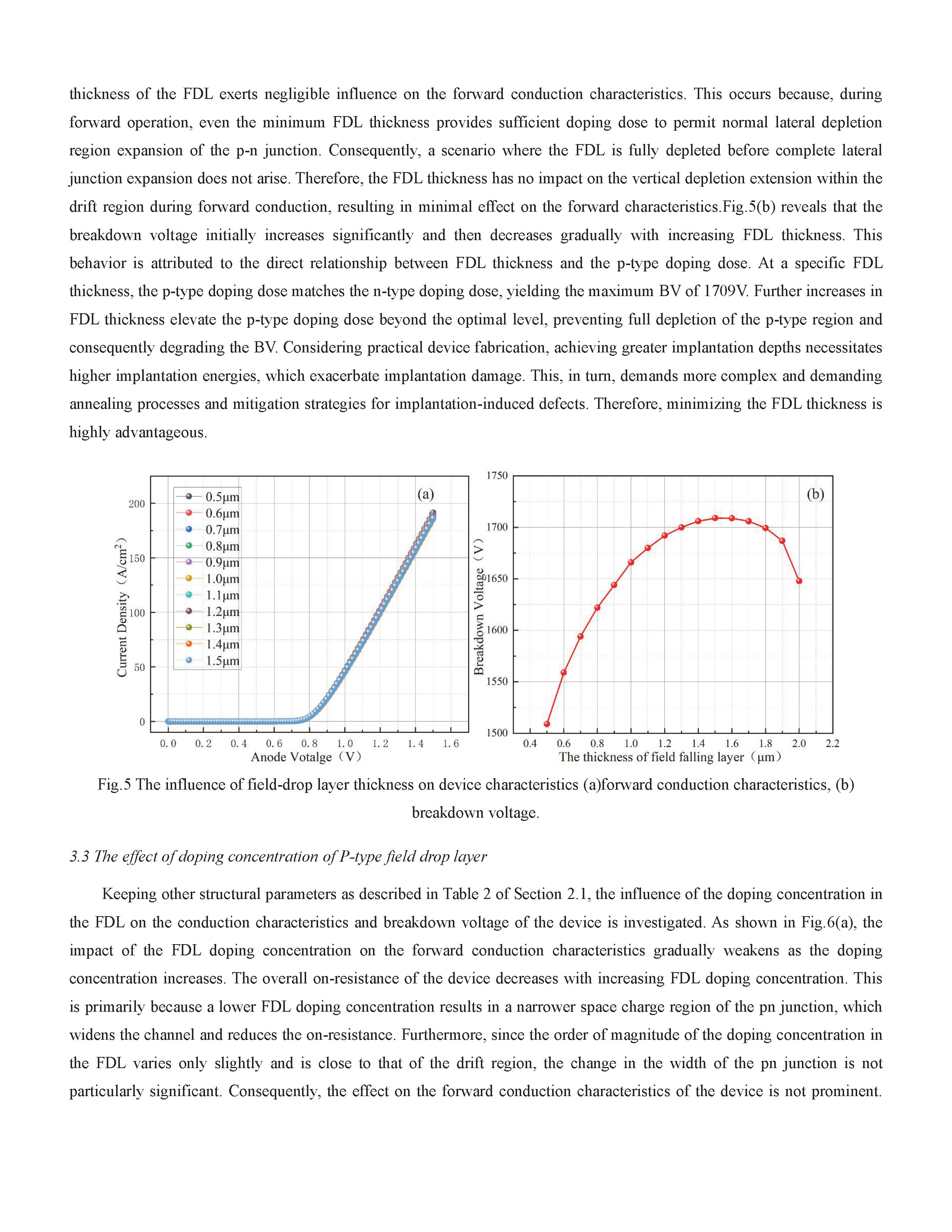

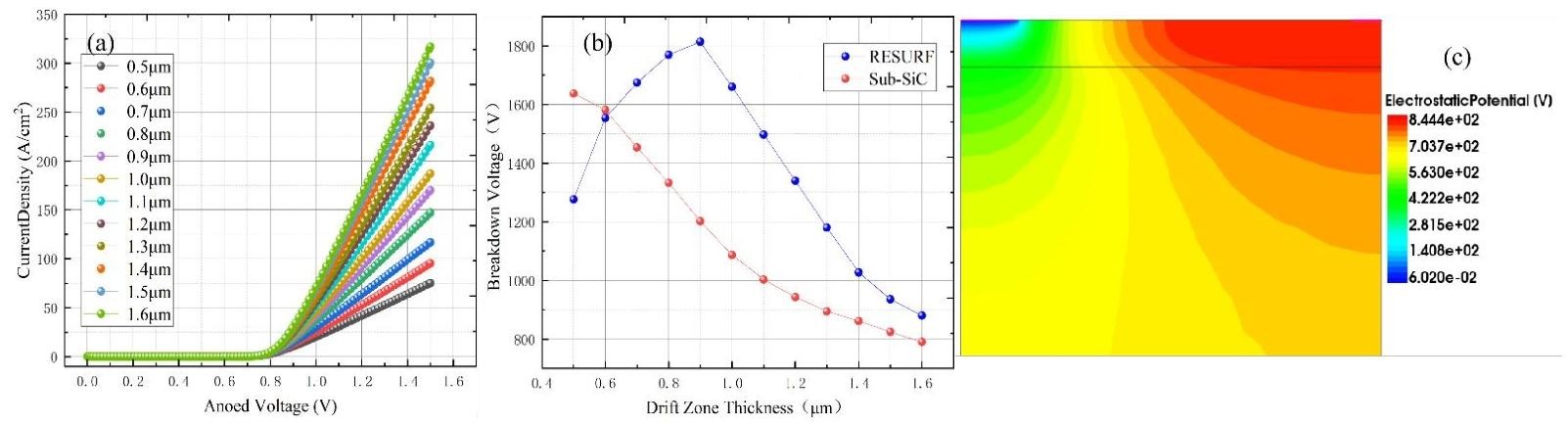

图4. 漂移层厚度对器件性能的影响:(a) 正向导通特性;(b) 击穿电压;(c) 厚度为 1.6 μm 时击穿状态下的静电势分布。

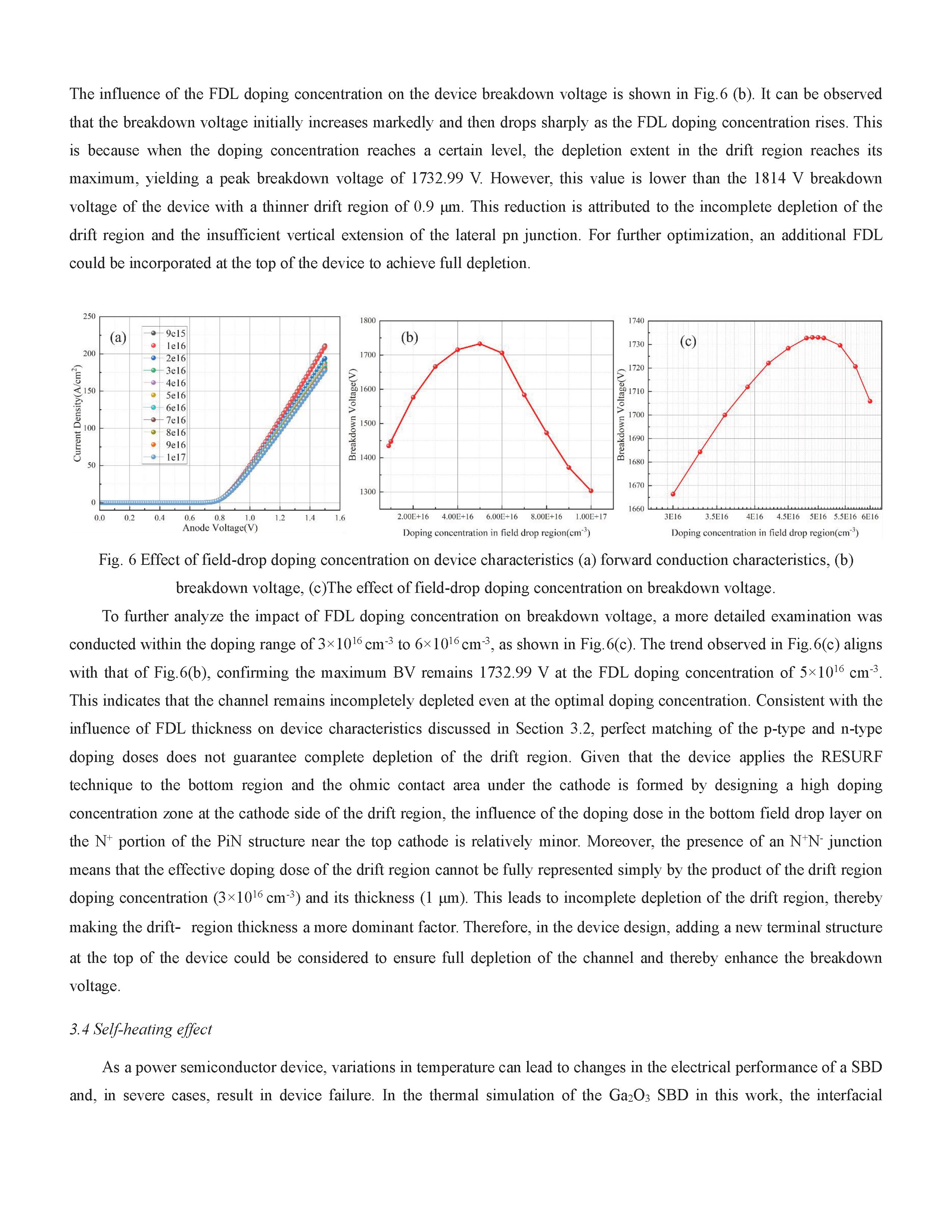

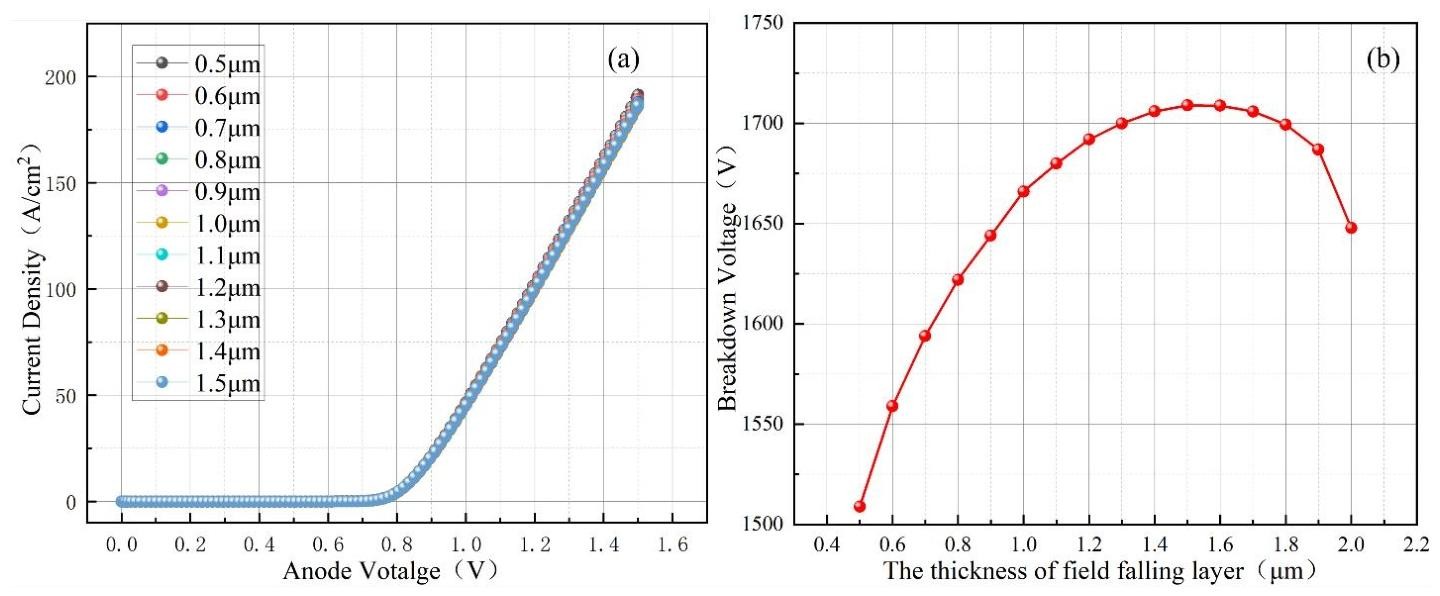

图5. 降场层厚度对器件特性的影响:(a) 正向导通特性;(b) 击穿电压。

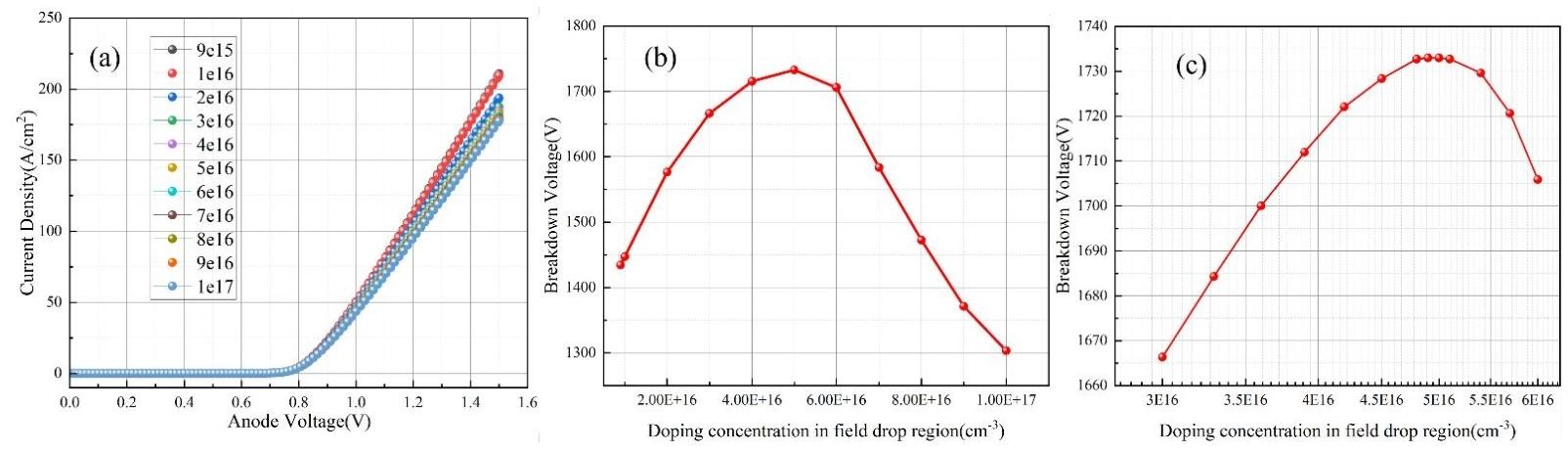

图6. 降场层掺杂浓度对器件特性的影响:(a) 正向导通特性;(b) 击穿电压;(c) 降场层掺杂浓度对击穿电压的影响。

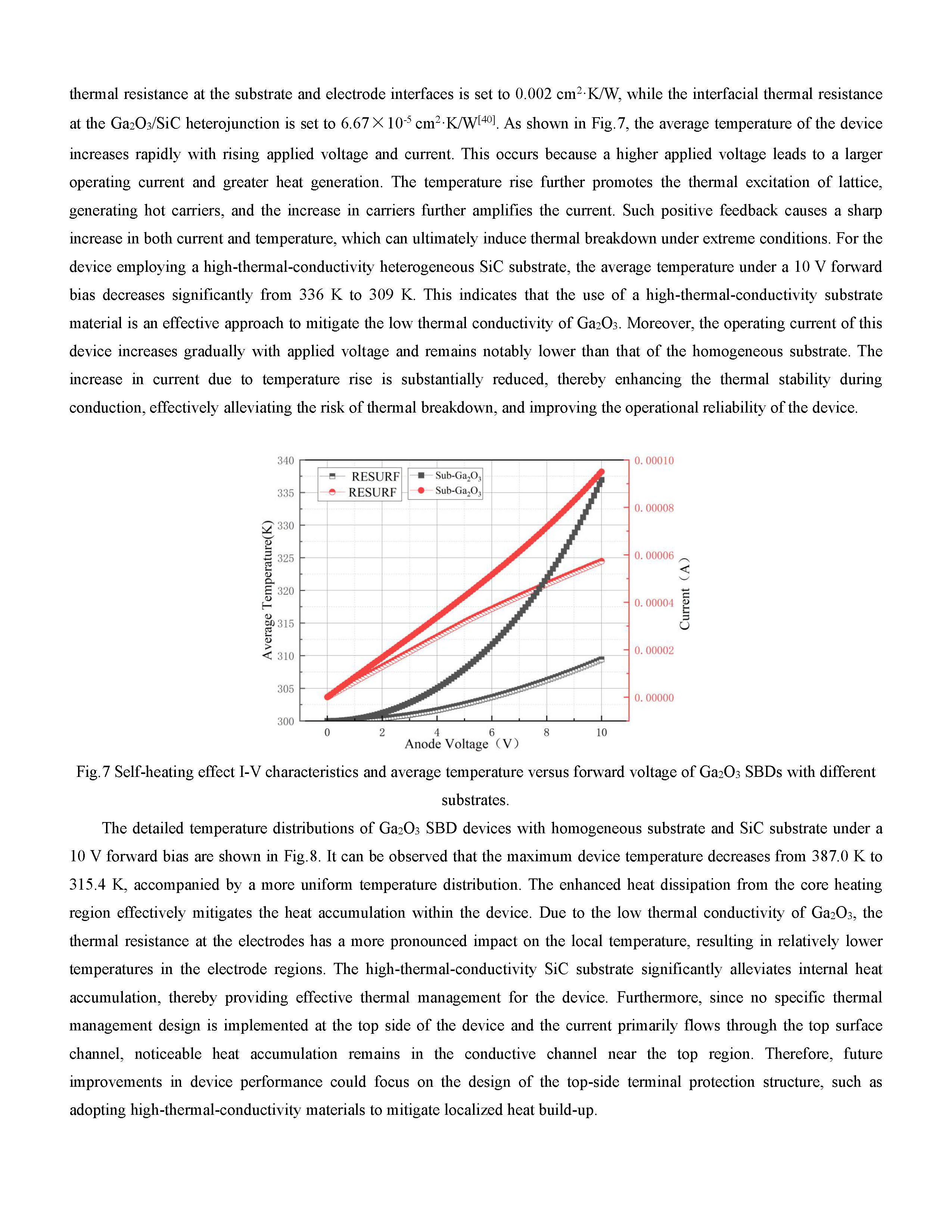

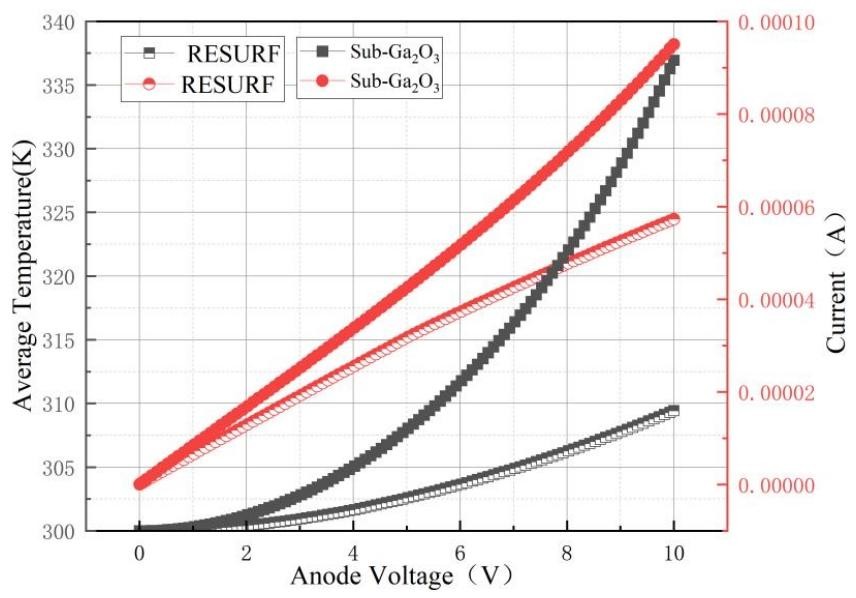

图7. 不同衬底的 Ga₂O₃ 肖特基势垒二极管的自热效应 I-V 特性与平均温度随正向电压的变化关系。

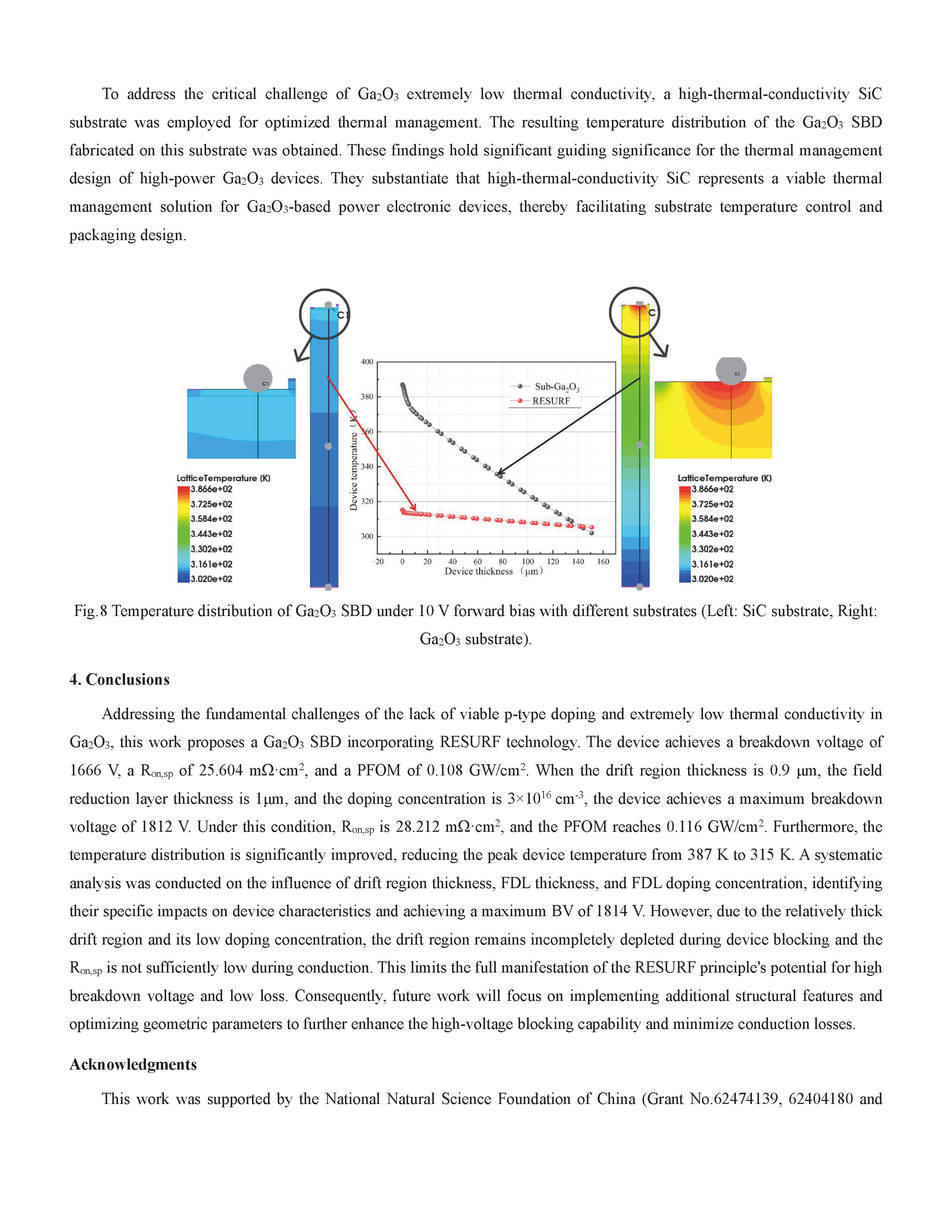

图8. 10 V 正向偏置下不同衬底的 Ga₂O₃ 肖特基势垒二极管温度分布(左:SiC 衬底;右:Ga₂O₃ 衬底)。

DOI:

doi.org/10.1016/j.mejo.2026.107173