【国内论文】北京理工大学王业亮教授团队---通过共溅射技术实现高性能掺锡 Ga₂O₃ FET: 耗尽模式与增强模式

日期:2025-04-21阅读:672

由北京理工大学的研究团队在学术期刊 Materials Science in Semiconductor Processing 发布了一篇名为 High-performance Sn-doped Ga2O3 FETs by co-sputtering: Depletion mode versus enhancement mode(通过共溅射技术实现高性能掺锡 Ga2O3 FET: 耗尽模式与增强模式)的文章。

项目支持

该研究得到国家重点研发计划(2023YFB3611700)和国家自然科学基金(92163206, 12321004)的资助。

背景

氧化镓(Ga2O3)作为一种超宽禁带半导体,具有高击穿场强(~8 MV/cm)和高巴利加优值(BFOM > 3000),在电力电子领域具有巨大潜力。通过掺杂(如 Sn, Ge, Si)可以有效提高 Ga2O3 场效应晶体管(FET)的载流子浓度和导电能力。Sn 掺杂能显著提高 Ga2O3 FET 的开态电流(ION),但通常导致器件工作在耗尽型模式(d-mode)。对于功率应用,增强型模式(e-mode)器件因其安全性和低功耗特性而更受欢迎。实现 e-mode Ga2O3 FET 存在挑战,现有方法或牺牲器件性能(如降低 ION),或增加工艺复杂度和成本(如 FinFET、垂直结构)。传统 Ga2O3 器件制备常需高温和特定衬底,限制了模式调控的灵活性和大规模生产的可行性。物理气相沉积(PVD)法,如溅射(特别是共溅射),为 Ga2O3 器件制造提供了低成本、低温、工艺简单、易于掺杂、可大面积生产且与硅工艺兼容的途径。

主要内容

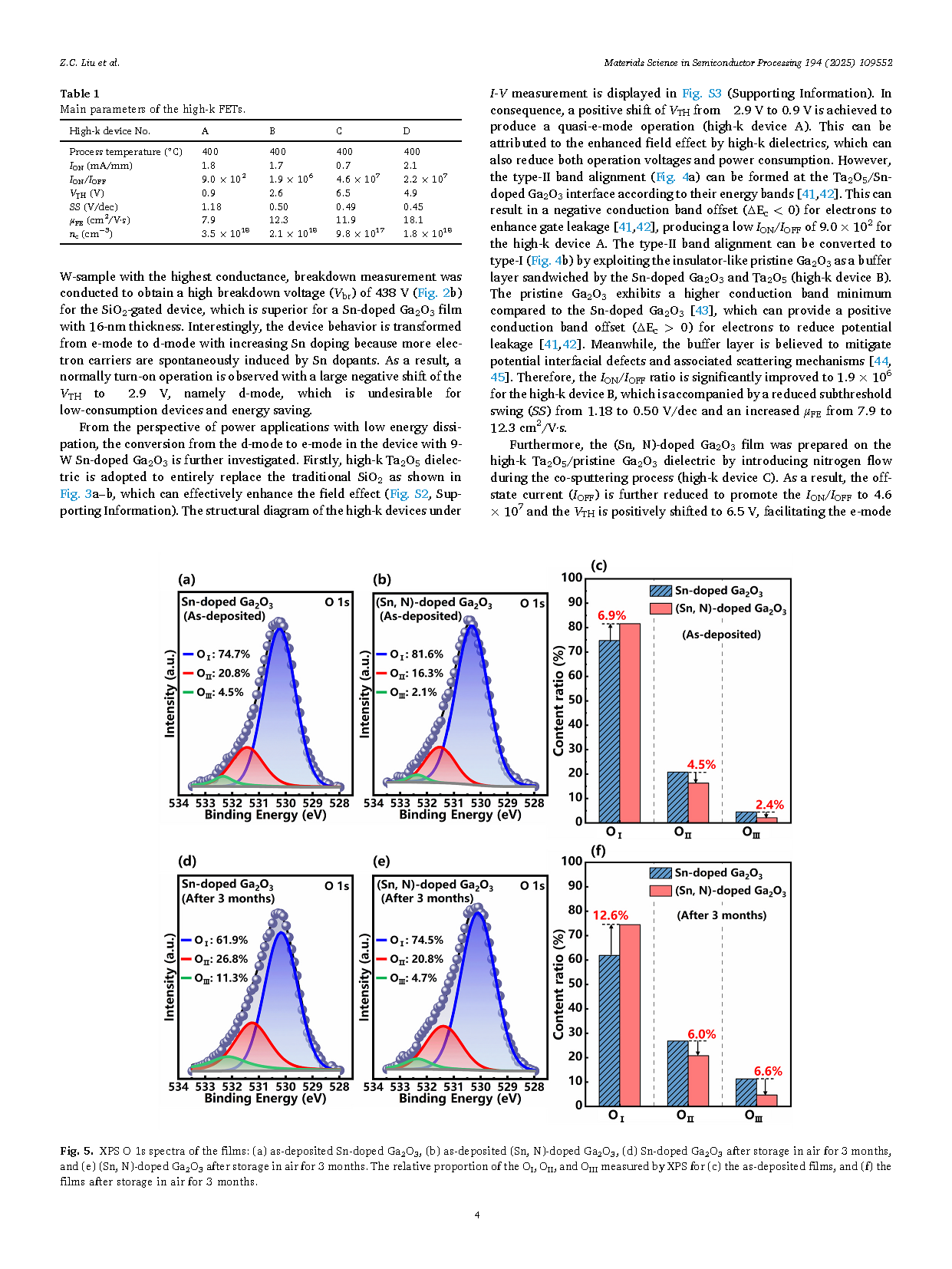

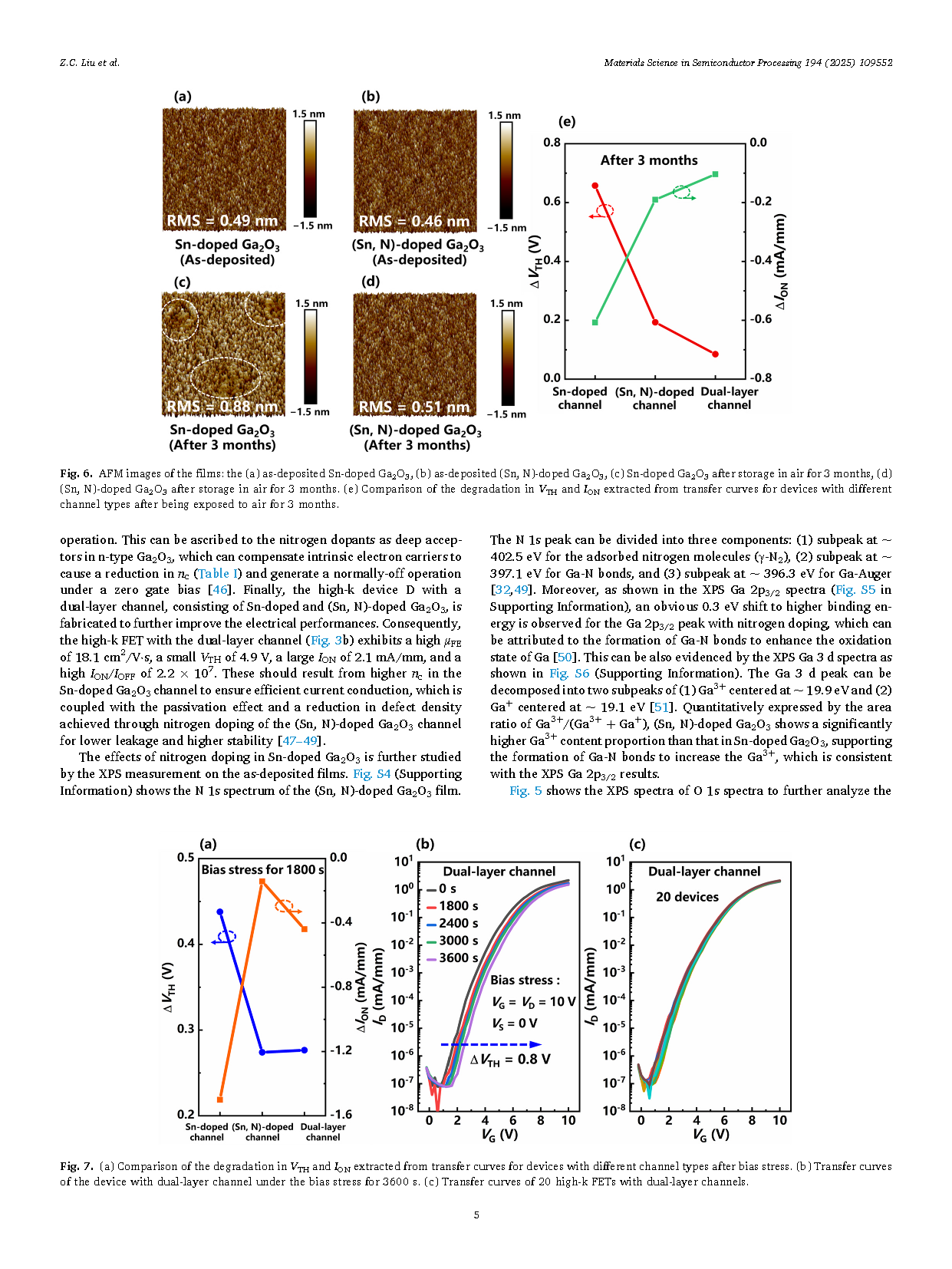

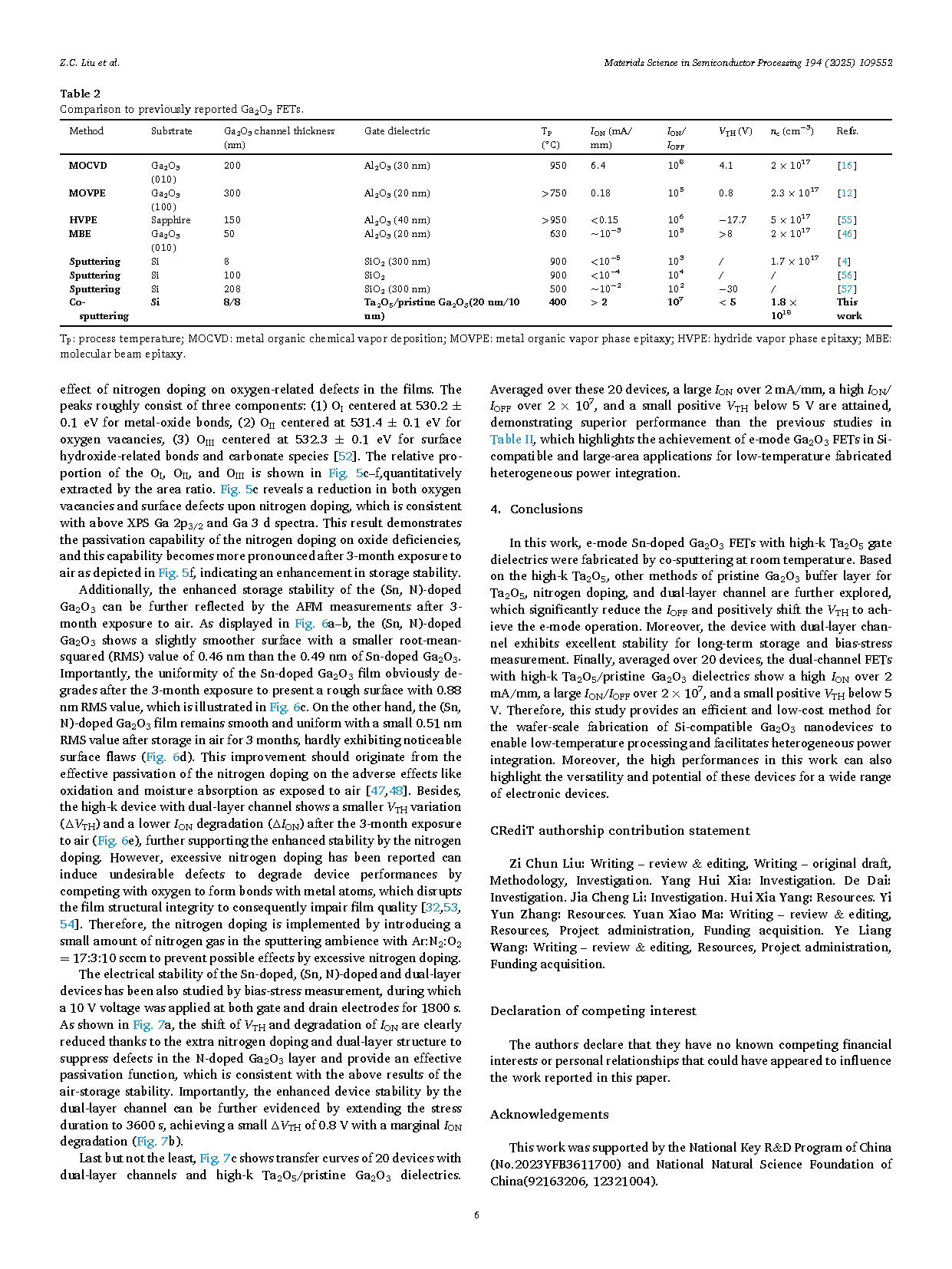

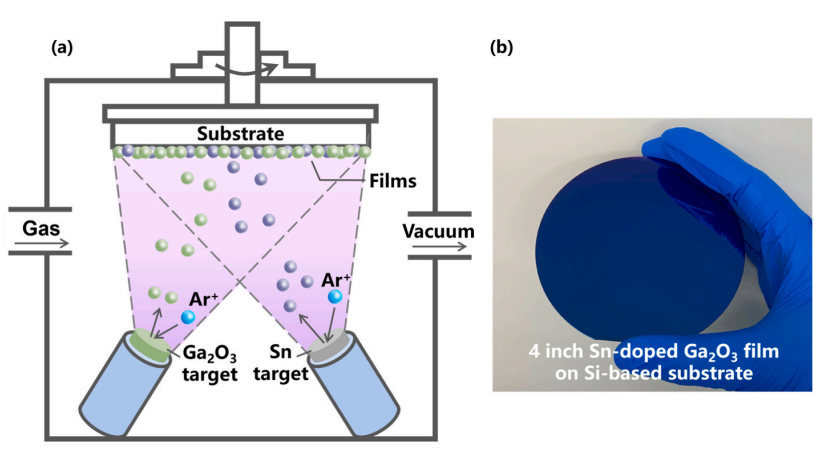

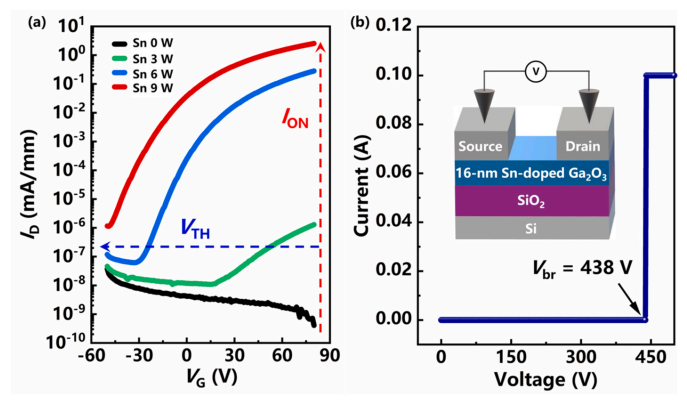

通过室温共溅射法在 Si/SiO2 衬底上沉积了高性能的掺锡氧化镓(Ga2O3)薄膜,以制造场效应晶体管(FET)。通过改变共溅射的锡功率来优化 SiO2 支撑的 FET 性能,实现了 2.5 mA/mm 的大导通电流(ION)和超过 106 的高开/关比。然而,这伴随着负阈值电压(VTH)的常开行为,即耗尽模式(d-mode)。重要的是,通过采用高介电常数的 Ta2O5/原始 Ga2O3 介质以及在掺锡 Ga2O3 沟道中额外掺入氮(N),可以将这种 d-mode 转换为增强模式(e-mode)。最后,通过采用掺锡 Ga2O3/(锡、氮)掺杂 Ga2O3 双层沟道结构,可以提升高介电常数介质的 e 模式 FET 的性能,其 ION 超过 2 mA/mm,开/关比超过 107,VTH 小于 5 V。此外,双层沟道的 FET 显示出出色的稳定性,这从偏置应力测量和暴露于空气中 3 个月后的稳定性能中得以体现。这种显著提升的性能归因于高介电常数电介质增强的场效应,以及双层沟道结构,该结构兼具(Sn,N)掺杂层的高稳定性和 Sn 掺杂层的高电流能力。

研究亮点

• 通过共溅射法制造出了高性能的掺锡 Ga2O3 场效应晶体管。

• 已成功实现从耗尽模式到增强模式的转换。

• 通过开发(Sn,N)掺杂的 Ga2O3/Sn 掺杂的 Ga2O3 双层通道,获得了出色的稳定性。

总结

在该项工作中,通过室温共溅射技术制备了具有高介电常数 Ta2O5 栅极绝缘层的 e-mode 掺锡 Ga2O3 场效应晶体管。基于高介电常数 Ta2O5,进一步探索了原始 Ga2O3 缓冲层、氮掺杂和双层沟道等方法,显著降低了 IOFF,并使 VTH 正向偏移,从而实现了 e 模式操作。此外,双层沟道器件在长期存储和偏置应力测量中表现出优异的稳定性。最后,对 20 个器件取平均值,具有高介电常数 Ta2O5/原始 Ga2O3 绝缘层的双层沟道 FET 显示出 ION 超过 2 mA/mm 的高值,ION/IOFF 超过 2×107 的大值,以及低于 5 V 的小正 VTH。因此,这项研究为硅兼容 Ga2O3 纳米器件的晶圆级高效低成本制造提供了一种方法,以实现低温处理,并促进异质功率集成。此外,该研究中的高性能也突显了这些器件在广泛电子设备中的多功能性和潜力。

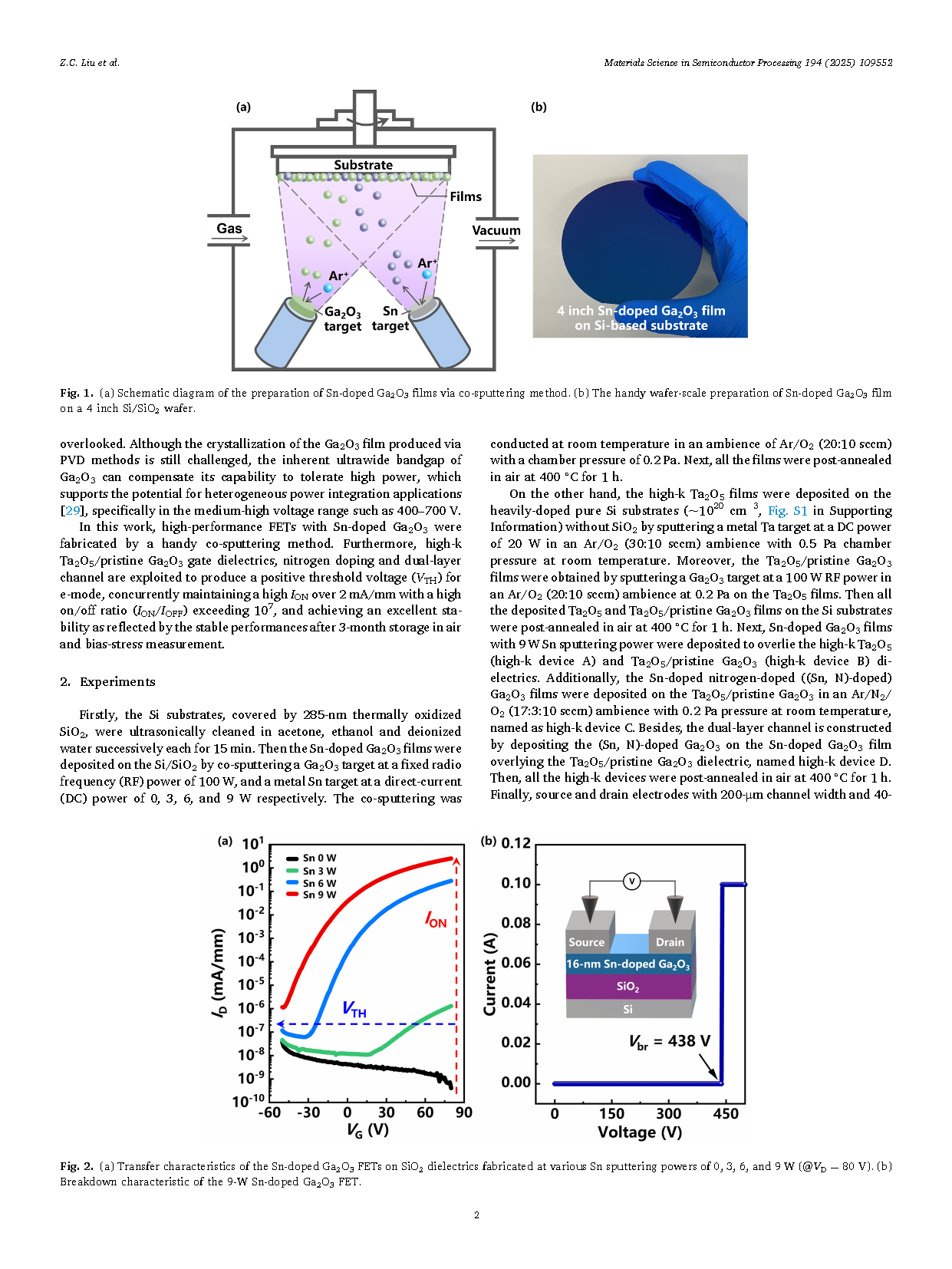

图 1. (a) 通过共溅射法制备掺锡 Ga2O3 薄膜的示意图。(b) 在 4 英寸 Si/SiO2 晶圆上方便地制备掺杂锡的 Ga2O3 薄膜。

图 2. (a) 以 0、3、6 和 9 W 的不同锡溅射功率(@VD = 80 V)在 SiO2 电介质上制造的掺锡 Ga2O3 FET 的传输特性。(b) 9 W 锡掺杂 Ga2O3 FET 的击穿特性。

DOI:

doi.org/10.1016/j.mssp.2025.109552